## 卒業研究報告

題 目

## 同期式順序回路の設計

指導教員

矢野 政顕 教授

報告 者

小島 大輔

平成 13 年 2 月 22 日

## 高知工科大学 電子・光システム工学科

# 目次

| 第  | <b>§</b> 1 | 章  |      | は  | じ  | め  | に  | • | • | •        | • | •  | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | •   | •   | 2          |

|----|------------|----|------|----|----|----|----|---|---|----------|---|----|----|----------|----|-----|---|---|---|---|---|---|----------|---|----|---|---|---|---|---|-----|-----|------------|

|    |            | 章  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

| 2. | . 1        | 順  | 涥    | 奫  | 理  |    | 路  | • | • | •        | • | •  | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | •   | •   | 3          |

| 2. | . 2        | 状  | 態    | 遷  | 移  | 表  | لح | 状 | 態 | 遷        | 移 | 巡  | •  | •        | •  | •   | • | • | • |   | • | • |          | • | •  | • | • | • | • | • | •   | •   | 4          |

| 2. | . 3        | フ  | עו י | ッ  | プ  | ゚フ | П  | ツ | ブ | 回        | 路 |    | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | •   | •   | 5          |

| 2. | . 4        | 力  | ウ    | ン  | タ  |    | 路  | • | • | •        | • | •  | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | •   | •   | S          |

|    |            | 章  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    |            | 標  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    |            | ナ  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    |            | F  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

| 3. | . 4        | Ē  | 計    | †伢 | IJ | ~  | カ  | Ċ | ン | <b>/</b> | ゝ | ブヴ | フン | /日       | 寺言 | † ~ | _ | • | • | • | • | • | •        | • | •  | • | • | • | • | • | ,   | • 2 | <u>?</u> C |

|    |            | 章  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    |            | 1  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    |            | 2  |      |    |    |    |    |   |   |          |   |    |    |          |    |     |   |   |   |   |   |   |          |   |    |   |   |   |   |   |     |     |            |

|    | 4.         | 3  | V    | Η  | D  | L  | に  | よ | る | 順        | 序 | 回  | 路  | <b>の</b> | 設  | 計   | 例 |   |   | カ | ウ | ン | <b> </b> | タ | ゛ウ | ン | 诗 | 計 | - | • | , , | • 3 | 37         |

| 第  | <b>§</b> 5 | 章  |      | お  | わ  | IJ | に  | • | • | •        | • | •  | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | , , | • 5 | 55         |

| 諺  | 秳          | ¥• | •    | •  | •  | •  | •  | • | • | •        | • | •  | •  | •        | •  | •   | • | • | • | • | • | • | •        | • | •  | • | • | • | • | • | , , | • 5 | 56         |

| 参  | 津          | 文  | 献    | •  | •  | •  | •  |   |   |          | • | •  |    | •        | •  | •   | • | • |   | • | • | • | •        | • | •  | • | • | • | • | • |     | • 5 | 57         |

## 第1章 はじめに

最近ではパソコンに限らず身のまわりのちょっとした電気製品にまで 想像以上の集積回路が組み込まれている。これらの集積回路がどのように 設計されどのように動作しているかなどの興味から、ディジタル回路に対 する理解を少しでも深めることができればと思い、この課題に取り組むこ とにした。

実際には短時間で一度に理解することができないので、ディジタル基本 回路のひとつである順序回路の仕組みと設計を、カウントダウン時計の製 作を通して学んだ。

本報告の第2章では、順序論理回路の設計に関する基本事項をまとめている。第3章では、標準論理ICを使用した順序論理回路の設計について述べ、第4章では、新しい設計方法であるハードウェア記述言語による設計方法について述べている。最後に第5章で卒業研究の成果をまとめている。

## 第2章 順序論理回路

## (sequential logic circuits)

## 2.1 順序論理回路

論理回路は時間に関係しない回路と時間に依存する回路に大別できる。時間に関係なく、与えられた入力値から出力値が一意的に決まる回路が**組み合わせ回路**である。

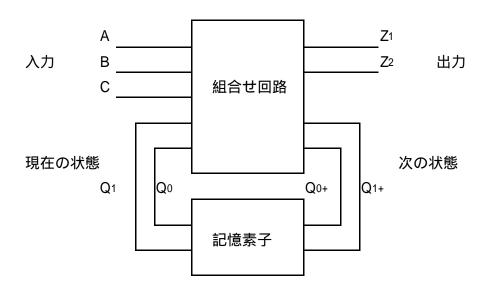

順序論理回路(sequential logic circuits)は、入力だけでなく過去の入力によって得られた現在の状態にも影響されて次の状態と出力が決まる回路である。順序回路の概念図を図 1.1 に示す。過去の状態をフィードバックして記憶素子に記憶させ、それを現在の状態(内部状態:internal state)とする。順序回路はこの現在の状態と入力を組み合わせ回路に入力して次の状態と出力を得るもので、組み合わせ回路と記憶素子で構成されるものである。順序回路を最も簡単に理解できる典型的な例がカウンタである。例えば現在の状態が3の時、次の入力1があれば次の状態が4になり、現在の状態によって次の状態が異なることが分かる。

図 2.1 順序回路の概念図

図 2.1 において、入力A、B、Cと現在の状態Qo、Q1の組み合わせで出力関

数 $Z_0$ 、 $Z_1$  および次の状態 $Q_0+$ 、 $Q_1+$  が求まる。順序回路に使用する1 ビットの記憶素子を**フリップフロップ**(flip-flop: FFと略記する)といい、動作の異なるいろいろな種類がある。出力 $Z_0$ 、 $Z_1$  を求める方法は従来の組み合わせ回路の設計順序と同じだが、現在の状態を記憶させるために使用するFFの動作が異なるので $Q_0+$ 、 $Q_1+$  が異なる。順序回路の設計とは、入力A、B、Cと現在の状態 $Q_0$ 、 $Q_1$  を順序回路の入力変数とし、次の出力 $Z_0$ 、 $Z_1$  および同時に得られた次の状態をFFに正しく記憶させるための $Q_0+$ 、 $Q_1+$  を求めることである。したがって、記憶素子として使用するFFの動作特性とその制御方法について理解しなければならない。

記憶素子(memory:メモリ)のことを遅延素子(delay)ともいう。この遅延時間を発生させる方法として、外部から動作時点を指定するクロックパルス(clock pulse:cp と略記する)を用いる同期式(synchronous)および素子の伝搬遅延時間(信号が素子に入力してから出力されるまでの時間)を利用する非同期式(asynchronous)がある。前者は動作速度がクロックパルスに依存するが、現在の状態が十分安定したと思われる時間間隔で動作されるので安定性がよく、コンピュータなどの設計に用いられる。後者は、原理的に前者よりは高速だが、回路が複雑になると遅延時間の推定が困難になるので、むしろ時間に左右されない比較的遅いディジタル回路設計に使われる。

### 2.2 状態遷移表と状態遷移図

組み合わせ回路ではその設計に真理値表を用いたが、順序回路では真理値表の代わりに**状態遷移表**(state transition table)を用いる。順序回路は安定した現在の状態に入力信号が加わると出力が出るとともに次の状態へ遷移する。この移りゆく状態を表にしたものを状態遷移表といい、理解しやすくするために図示したものを**状態遷移図**(state transition diagram)という。

| C Z.I NOZEDK |       |      |    |  |  |  |

|--------------|-------|------|----|--|--|--|

| 入力           | 現在の状態 | 次の状態 | 出力 |  |  |  |

| 0            | S0    | S0   | 0  |  |  |  |

| 1            | S0    | S1   | 0  |  |  |  |

| 0            | S1    | S1   | 0  |  |  |  |

| 1            | S1    | S2   | 0  |  |  |  |

| 0            | S2    | S2   | 0  |  |  |  |

| 1            | S2    | S0   | 1  |  |  |  |

表 2.1 状態遷移表

## 2.3 フリップフロップ(FF)

順序回路を構成する重要な部品である記憶素子(メモリ)は、通常多数のラッチ(latch)やフリップフロップと呼ばれるものによって構成されている。ラッチやFFは1ビットの記憶素子であり、いくつかの種類がある。FFの状態変化(クロックを含む)は入力による。ある論理値とその論理が逆の値の両方(これを相補(complementary)信号と言う。)を出力することができる。FFのほとんどはセットとリセットの機能が付加されており、これらはFFでレジスタやカウンタを構成した時に、その初期値の設定に使用される。

## 2.3.1 SRフリップフロップ

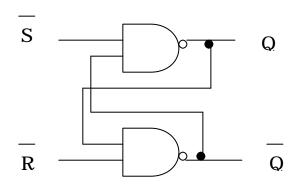

**SR-FF**(set reset)は2個のNAND素子で構成される最小構成のFFである。実際のFFは、SR-FFの機能と他の3つのFFを組み合わせたものがほとんどである。FFとは図2.2に示す**2安定マルチバイブレータ**(multi vibrator)のことである。マルチバイブレータにはこの他に無安定(安定のない発信器)と1安定(安定点が1つある単発パルス発信器)があり、いずれも実用ディジタル回路ではよく使用される。

図 2.2 2 安定マルチバイブレータ

図 2.3 SR - FF の記号

表 2.2 SR - FF の遷移表

| 入力  | 現在の状態 | 次の状態     |

|-----|-------|----------|

| S R | Q     | Q'       |

| 0 0 | 0     | 0        |

| 0 0 | 1     | 1        |

| 0 1 | 0     | 0 (リセット) |

| 0 1 | 1     | 0 (リセット) |

| 1 0 | 0     | 1 (セット)  |

| 1 0 | 1     | 1 (セット)  |

| 1 1 | 0     | ×        |

| 1 1 | 1     | ×        |

SR-FFの**セット**とはQ端子から 1 を出力させることで、**リセット**とはQ端子から 0 を出力させることである。外部からSまたはRに入力しない限りは永久にQから1または0のいずれかの出力状態(2つの安定状態)を維持する。この 2 つの安定状態は、Q端子から 1 が出ている時はFFが 1 を記憶し、0 が出ている時は0を記憶していることを意味している。

## 2.3.2 Tフリップフロップ

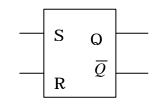

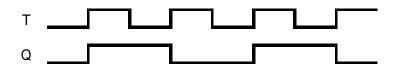

**T-FF**(toggle/trigger)とは、T入力があるたびにQ出力が反転動作をする(トグル動作という)FFである。これは1ビットの2進カウンタに相当する。そのタイミングチャートを図2.4に、また遷移表を表2.3に示す。

図 2.4 T-FFのタイミングチャート

| 表 2.3 T-FFの遷移      |    |

|--------------------|----|

|                    | =  |

|                    | ┺- |

| 衣 2.3 I-FF の 達 移 4 | v  |

| 入力 T | 現在の状態 Q | 次の状態 Q' |

|------|---------|---------|

| 0    | 0       | 0       |

| 1    | 0       | 1 反転    |

| 0    | 1       | 1       |

| 1    | 1       | 0 反転    |

FFは一般にSR-FFの機能であるセットとリセット端子を兼備している。これらは**ダイレクトセット**(SD)または**プリセット**(PR)および**ダイレクトリセット**(RD)または**クリア**(CLR)などと呼ばれている。

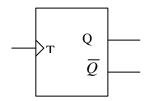

T-FFの記号を図 2.5 に示す。

図 2.5 T-FFの記号

### 2.3.3 JKフリップフロップ

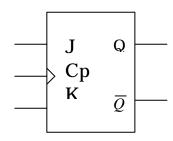

**JK-FF**は、SR-FFに cp を追加して SR-FF の禁止入力 SR=0 を改善したものである。J/K 入力のいずれかが " 0 " のとき、SR フリップフロップと同じ動作をし、J/K 入力ともに " 1 " のとき、Q 出力が反転(F グル)という動作をする。SR-FF は、S、R に同時に入力することを禁止しているが、JK-FF は J、K に同時に入力した場合でも Cp に同期して安定した出力が得られる。SR-FF や D-FF の機能を包含しているので、それらよりも適用範囲は広い。

図 2.6 JK - FF の記号

表 2.4 JK - FF の遷移表

| 入力  | 現在の状態 | 次の          | 状態          |

|-----|-------|-------------|-------------|

| J K | Q     | Q' (Cp = 1) | Q' (Cp = 0) |

| 0 0 | 0     | 0           | 0           |

| 0 0 | 1     | 1           | 1           |

| 0 1 | 0     | 0 (リセット)    | 0           |

| 0 1 | 1     | 0 (リセット)    | 1           |

| 1 0 | 0     | 1 (セット)     | 0           |

| 1 0 | 1     | 1 (セット)     | 1           |

| 1 1 | 0     | 1 (反転)      | 0           |

| 1 1 | 1     | 0 (反転)      | 1           |

## 2.3.4 Dフリップフロップ

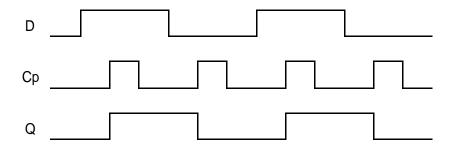

**D-FF** (delay/data latch) は c pに同期して c pが入力する直前の D入力の状態と同じ状態を Q から出力するものである。タイミングチャートを図 2.7 に、遷移表を表 2.5 に示す。常に c p = 1 の時動作するので、この表では c pを省いている。表から D-FF の特性方程式は次式になる。

$$Q' = DQ + D\overline{Q} = D$$

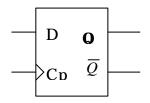

また、D-FFの記号を図 2.8 に示す。

図 2.7 D-FF のタイミングチャート

表 2.5 D - FF の遷移表

| D | Q | Q' |

|---|---|----|

| 0 | 0 | 0  |

| 0 | 1 | 0  |

| 1 | 0 | 1  |

| 1 | 1 | 1  |

図 2.8 D-FF の記号

## 2.3.5 マスタースレーブ型フリップフロップ

状態変化がクロックパルスの立ち上がり(ポジティブエッジ)/立下り(ネガティブエッジ)によって生じるFFを**エッジトリガ型フリップフロップ**という。クロックの立ち上(下)がり(マスタ)と立ち下(上)がり(スレーブ)の組で1つの動作(2段階動作)を行うFFを**MS型FF**という。動作タイミングが異なるだけで、種類はエッジトリガ型フリップフロップと同様なものがある。

### 2.4 カウンタ

カウンタ (counter) は、単に計数回路としてだけではなく、タイマ回路や分周回路、さらには計算機の制御、モーターの回転数の計算、時計など非常に広く用いられています。

カウンタはパルスの数を計数し、記憶する回路で、その動作方式から非同期式 (asynchronous)と同期式 (synchronous)に大別される。基本となる回路素子として、FFが用いられる。

### 2.4.1 同期式カウンタ

非同期式カウンタの問題点は、カウント数が大きくなれば遅延時間が蓄積されていくことである。この欠点を解決するのが同期式カウンタで、すべてのFFのクロック端子を共通のクロックで一斉に制御できるようになっている。そ

の結果、伝搬遅延時間はFFの段数に関係なく最も応答の遅いFF1個分の遅延ですむ。しかしFFの段数が多くなるとクロックのファンアウト数が増え、クロック入力のインピーダンスが減少するので波形ひずみの原因になりやすい。すべてのFFがクロックに同期して動作する同期式カウンタはすべてのFFが並列動作することから並列カウンタともいう。

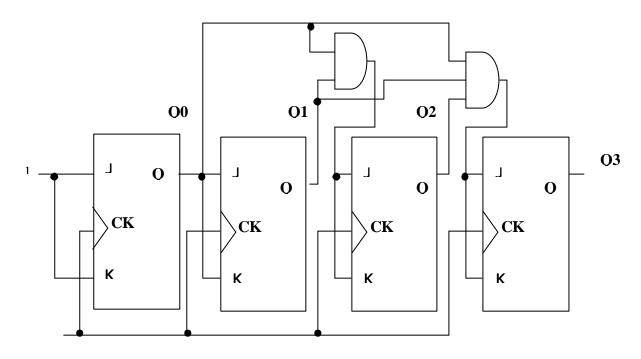

参考として図 2.9 に J K - F F による同期式 4 ビット 2 進力ウンタの例を示す。

図 2.9 JK-FFによる同期式 4 ビット 2 進力ウンタ

## 2.4.2 同期式と非同期式

どちらの方式を選択するかは用途によって選択する必要がある。一般的には 同期式カウンタの方が問題は少ない。非同期式カウンタは回路構成が簡単であ る利点はあるが、前段のフリップフロップ出力が、後段のクロック入力となっ て次々に伝えられるため、伝搬遅延時間を考慮しなければならない。一方、同 期式カウンタは入力パルスを全フリップフロップのクロックに共通に接続する 形式であるため伝搬遅延時間は少ない。

また、非同期式カウンタでは、各フリップフロップの出力をデコードするとスパイク状のノイズが発生することがある。このノイズは回路の誤動作になることが多い。一方、同期式カウンタでは、各フリップフロップが同時に変化するため、出力をデコードしてもノイズは発生しにくい。

## 2.4.3 可逆カウンタ

カウントアップ(カウント数の増加、インクリメント)のカウントダウン(カウント数の減少、デクリメント)の両方が可能なカウンタを可逆カウンタ(アップダウンカウンタ)という。

## 第3章 標準論理ICによる回路設計

## 3.1 標準論理 I C

初期の IC は超小型の電子部品をモジュールとして組み合わせたもので、1970年代以降は、コンデンサやトランジスタ回路などを 1 つのチップ上に形成する半導体 IC が主流となった。半導体 IC は、形成されるトランジスタのタイプの違いによりバイポーラ型と MOS 型とに分類される。さらに最近ではバイポーラ型とMOS 型とを組み合わせた I C も開発されている。

## 3.1.1 バイポーラ型 IC

バイポーラとは「2つの極性」という意味で、電子と正孔(ホール)の2つがIC内部の電流の運び手(キャリア)になっているため、こう呼ばれる。

トランジスタが動作状態にあるとき、素子の中を電流が流れるメカミズムに着目し、電子または正孔のどちらか一方だけがキャリアとして動作しているものをユニポーラ(単極性)と呼び、MOS型トランジスタがこれにあたる。電子と正孔の両方がキャリアとして動作しているものをバイポーラ型トランジスタと呼ぶ。

#### 3.1.2 MOS型IC

MOS 型とは、Metal (金属)・Oxide (酸化膜)・Semi-conductor(半導体)の頭文字の略である。この略号そのものが構造を表し、半導体基板の表面に薄いシリコン酸化膜を作り、その上に金属電極(ゲート)をつけたもので、このゲートにかける電圧によって半導体の機能が制御される。

MOS 型は、構造が簡単で高集積化に適しており、小さな電力で動作するのが特長である。特に CMOS(Complementary = 相補形 MOS)タイプは、消費電力が低いため、現在製造されている MOS 型 IC のなかの主流となっている。

MOS 型 IC を機能面で分類すると、メモリ(記憶素子)とロジック(論理素子)の2つに分かれる。

## メモリ(記憶素子)

膨大な量の計算結果やその途中のデータなどの情報を記憶する。メモリはさらに、RAM(書き込み読み出しメモリ)と ROM(読み出し専用メモリ)とに大別できる。

## ロジック(論理素子)

演算処理を行う役目の IC で、各種の計算をしたり、情報と情報を比べたり、他の IC などのコントロールを行う。ロジックは、さらにマイクロプロセッサや周辺 LSI などのマイコンと、専用ロジックに分類できる。

このほかにバイポーラ型とユニポーラ型の両方の利点を活かすため、これらを混在させたBiCMOSディジタルICも開発されたが、製造プロセスが複雑であること、CMOSに比べ性能面の利点が少ないということで現在では殆ど作られていない。

### 3.1.3 標準論理ICファミリ

標準論理ICは、メーカーが違っても電気的な特性が同じように作られた一連の仲間を持っており、それらをICファミリと呼んでいる。

汎用ロジックICのファミリにはいくつかの種類がるが、一般的に、ロー・パワー・ショットキーTTL(LS TTL)とCMOSの 74 H C シリーズおよび 4000/4500 シリーズが多く使われる。

ファミリ化されたICは、そのICに刻印されている型名を見れば製造したメーカーと機能が分かるようになっている。

例えば、74 シリーズのロー・パワー・ショットキーICである 74 L S の場合は、

英文字 数字 74 LS×××

と刻印されていれば、 の英文字がメーカー名を表し、LSがロー・パワー・ショットキー・ファミリであることを表し、×××の数字がICの機能を表している。×××が同じ番号のものであれば、型名表示(この場合LSと書かれた部分)によらず、同じ機能をもつように作られている。このため型名表示の部分を省略して、単に74×××と呼ぶことが多い。

英文字からわかるメーカー名の代表的なものを表 3.1 に、型名表示のファミリの例を表 3.2 に示す。

表 3.1 標準論理 I C製造メーカー名

| SN  | TI (テキサスインツルメント) |

|-----|------------------|

| MC1 | モトローラのCMOS製品     |

| CD  | RCAのCMOS製品       |

| MM  | NSのCMOS製品        |

| μPD | 日本電気のMOS製品       |

| TC  | 東芝のCMOS製品        |

| MB  | 富士通のデジタル IC      |

| HD  | 日立のデジタル 🏿        |

| DN  | 松下のデジタル℃         |

表 3.2 標準論理 I C 型名表示

| L   | ローパワーTTL               |

|-----|------------------------|

| S   | ショットキーTTL              |

| LS  | ローパワー・ショットキーTTL        |

| Н   | 高速 TTL                 |

| AS  | アドバンスト・ショットキーTTL       |

| ALS | アドバンスト・ローパワー・ショットキーTTL |

| HC  | 高速CMOS                 |

さらに標準論理IC型名表示についての特徴を表 3.3 に、COMS論理ICの型名表示についての特徴を表 3.4 に示す。

この他にBiCMOSファミリとして、74BCシリーズがある。

表 3.3 TTLファミリとその特徴

| 피      | カノー                | #±/#b                     |

|--------|--------------------|---------------------------|

| 型番     | タイプ                | 特徴                        |

| 74     | スタンダード             | 最初に開発されたTTL。              |

| 74 S   | ショットキー             | ショットキートランジスタを用いて高速化したもの。  |

| 74 AS  | アドバンスト・ショットキー      | 74 Sタイプを低消費電力化したもの。       |

|        |                    | スタンダードタイプに比べ低消費電力で、高速動作が可 |

| 74 LS  | ローパワー ショットキー       | 能。                        |

|        | アドバンスト・ローパワー・ショットキ |                           |

| 74 ALS | _                  | AS タイプをさらに低電力消費化したもの。     |

| 74 F   | FAST               | L S タイプに比べ低消費電力で高速化したもの。  |

表 3.4 СМОЅファミリとその特徴

| 型番        | タイプ         | 特徴                                                   |

|-----------|-------------|------------------------------------------------------|

| 4000/4500 |             | 最初に開発されたCMOS IC、74シリーズとは異なった<br>論理があり、低速だが電源電圧範囲が広い。 |

| 74 H C    |             | 低消費電力で TTLの L S タイプに匹敵する速度とファンアウトをもつ。                |

|           | ハイフピード      | CMOSとして標準的に用いられている。                                  |

| 74HCT     | //1 / C - 1 | HCタイプを、TTLとインタフェース可能にしたもの。                           |

| 74 AC     | FACT        | 低消費電力で TTLの F タイプに匹敵する速度とファンアウトをもつ。                  |

| 74 ACT    | IFACI       | A C タイプを、T T L とインタフェース可能にしたもの。                      |

## 3.2 カウンタ用IC

順序回路の設計にはカウンタICがよく用いられる。TTL ファミリーの代表的なカウンタICを表 3.5 に、また CMOS ファミリーの代表的なカウンタICを表 3.6 に示す。

表 3.5 TTLファミリーの 4 ビットカウンタ

| 型番      | 特徴                                   |

|---------|--------------------------------------|

| SN74160 | 4ビット、同期プリセット、非同期クリア                  |

| SN74161 | 4ビット、同期プリセット、非同期クリア                  |

| SN74162 | 4ビット、同期プリセット、同期クリア                   |

| SN74163 | 4ビット、同期プリセット、同期クリア                   |

| SN74168 | 4ビットBCD、同期プリセット、クリアなし、同期式可逆カウンタ      |

| SN74169 | 4 ビットバイナリ - 、同期プリセット、クリアなし、同期式可逆カウンタ |

| SN74190 | 4ビットBCD、非同期プリセット、クリアなし、同期式可逆カウンタ     |

| SN74191 | 4 ビットバイナリ - 、非同期プリセット、クリアなし、可逆カウンタ   |

|         | 4ビットBCD、非司期プリセット、非司期クリア、             |

| SN74192 | 同期式可逆カウンタ、並列入力                       |

|         | 4 ビットバイナリ - 、非同期プリセット、非同期クリア、        |

| SN74193 | 同期式可逆カウンタ、並列入力                       |

|         | 4ビットBCD、同期プリセット、同期/非同期クリア、           |

| SN74568 | 同期式可逆カウンタ、3ステート出力                    |

|         | 4 ビットバイナリ - 、同期プリセット、同期 / 非同期クリア、    |

| SN74569 | 同期式可逆カウンタ、3ステート出力                    |

| SN74390 | 非同期式、SN7490 × 2、プリセットなし              |

| SN74393 | 非同期式、SN7493 × 2、                     |

表 3.6 СМОЅファミリーの4ビットカウンタ

| 型番    | 特徵                                            |

|-------|-----------------------------------------------|

| 40102 | 同期式 4ビットBCD DOWN × 2、カスケード接続で拡張可能             |

| 40160 | 同期式 4ビット10進、非同期クリア端子付き                        |

| 40161 | 同期式、40160 のバイナリ - 型                           |

| 40162 | 同期式、40160 の同期クリア端子付き                          |

| 40163 | 同期式、40160 のバイナリ - 型で同期式クリア端子付き                |

| 40192 | 4ビットBCD UP/DOWNの独立したクロック入力、非同期リセット、プリセット機能    |

| 40193 | 4ビットバイナリ - UP/DOWNの独立したクロック入力、非同期リセット、プリセット機能 |

| 4526  | 同期式プログラマブル4ビットバイナリー、非同期プリセット / クリア            |

カウンタには、パルスの入力違いにより、同期式と非同期式とがある。同期 式は入力クロックに同期して各ビットの出力が変化するものであり、非同期式 は入力クロックに同期しないで各ビット出力が変わるものである。

また、これらのファミリーの中には、カウント・アップとカウント・ダウンの切り替えが出来るアップ / ダウン・カウンタ (可逆カウンタ) も含まれている。

さらに計数値により、2 進、4 進、8 進、16 進・・・などの 2 n 進力ウンタであるのがバイナリーカウンタ、BCD(Binary Coded Decimal number)、つまり 2 進化 10 進数を扱うBCDカウンタに分類できる。また計数の初期値を外部から設定できるのがプログラマブル・カウンタである。

カウンタの内部記憶回路であるフリップフロップやラッチは、JKまたはDフリップフロップであり、一般にクリア端子(リセット:CLR)とプリセット端子(セット:PR)を備えている。これらの入力信号は、クロック信号とは無関係に、強制的に信号をHレベル(プリセット)またはLレベル(リセット)にするもの(非同期式プリセットまた非同期リセット)とクロック信号に同期して出力信号をHレベル(プリセット)またはLレベル(リセット)にするもの(同期式プリセットまた同期式リセット)がある。

#### 非同期式PRまたはCLKは、

PRにLレベルを入力する(ピン配置図のPR端子に がついている)と、 出力Q=H、 $\overline{Q}$ =Lとなる。(アクティブロー:)

CLRCLVベルを入力する(アクティブロー:ピン配置図の<math>CLR端子にがついている)と、Q=L、 $\overline{Q}=H$ となる。

これら、 、 の設定期間中はクロック入力を無視し、PR,CLRの入力を解除(Hレベルにする)した後もその状態を保持する。

PR, CLRの両方を同時にLレベルにすると、Q、 $\overline{Q}$ ともHレベルを出力する。ただし、一方を先に解除すれば、出力の状態は、PRがLレベルのままであるか、CLRがLレベルのままであるかによって、またはに従って動作する。また同時に解除した場合は、素子のばらつきや、不可の大小によって、Q、 $\overline{Q}$ のいずれかがHレベルになるかは不定ある。

PR,CLRが両方とも解除(両方ともHレベル)となっていれば、クロック信号に従ってフリップフロップ本来の動作をする。

74160 と 74161 はクリア入力がクロックに非同期で、クロックに無関係でクリアできる例であり、74162 と 74163 はクリア入力がクロックに同期して、クリア端子(ピン配置図のCLR端子に がついている)がLレベルのときにクロックの立ち上がりでクリアできる例である。

## 3.3 PSpiceによる回路設計

SPICE は Simulation Program with Integrated Circuit Emphasis の頭文字をとったものでカリフォルニア大学バークレー校(UCB)で開発された回路解析プログラムです。その後いろいろな会社から発表され、代表的なものとしては、HSPICE (Meta Software)や PSpice (Cadence)、SPICE-Plus (ADT)、DSPICE (Daisy)、MSPICE (Mentor)などがあり、今回使用したのはCadence 社の PSpice A/Dである。

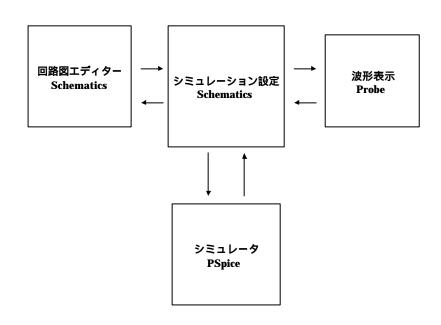

PSpice は主に 3 つの別々のソフトウェアからなり,構成は図 3.1 のようになっている。

図 3.1 PSpice のソフトウェア構成

## Capture

シミュレーションを行う元になる回路図を作成するプログラムで、シミュレーションの設定や、PSpice、Probe を有機的に結び付ける。

## **PSpice**

シミュレータ本体、回路データ(ネットリスト) 部品のデータ(モデルパラメータ) シミュレーション命令をアスキーファイルで入力しシミュレーションを行うプログラムである。

## Probe

シミュレーション結果をグラフにして表示するプログラムである。

回路設計のシミュレーションの流れはだいたい次のようになっている。

Capture で回路を設計する。

Capture でシミュレーションの内容,素子のパラメータを設定する。

PSpice でシミュレーションを実行する。

Probe で結果をグラフに表示する。

出力された結果が予定と違っていた場合はもう一度 に戻り回路の設計を やり直しシミュレーションし直す。

## PSpice によるシミュレーションの種類

PSpice で実行できるシミュレーションは大きく分けて3種類になる。PSpice はこれらのシミュレーションを行う前に必ずバイアスポイント解析という初期 値の計算を行う。

## ? バイアスポイント解析

PSpice でシミュレーションを実行する場合は前処理として必ず実行される。 バイアスポイント解析は以下のように回路をとらえる。

- キャパシタは解放する

- ・インダクタは短絡する

- ・時間に関する導関数を持つ素子の値は0にする

- ・半導体等はモデルを用いて線形化する

このような処理を行うことによって、どのような回路でも抵抗及び電圧源、 電流源のみで構成されるようになる。これによって、オームの法則、キルヒホ ッフの法則により回路中全てのノードの電流、電圧が計算できるようになる。

#### ? DC解析

DC解析はバイアスポイント解析と同様に回路をとらえる。しかし、バイアスポイント解析は 1 回だけ値を算出するのに対し、DC解析では回路上の電圧値、電流値及び素子の値のうちどれか一つを変動させその変動による電圧値、電流値を算出する。

出力は横軸が電圧、電流、素子値いずれかの静特性のグラフとなる。

### ? A C 解析

正弦波交流信号を入力として抵抗、キャパシタ、インダクタを複素数で展開されたインピーダンスとして取り扱う。入力正弦波信号の周波数を変化させて回路上の電圧、電流を伝達関数的に絶対値、デシベル、実数分、虚数分、位相の形で出力する。

ただし、線形領域の解析になるので入力信号の振幅の変化によるサチレーションの計算はできない。

横軸が周波数のグラフとなり、イメージ的にはスペクトラムアナライザー、ネットワークアナライザーと同じになる。

## ? **過渡解析** (Transient analysis)

過渡解析は、時刻ごとのノード電圧や電流を求める。バイアスポイント解析により初期状態を算出し、過渡的な回路動作を時間レンジで求める。過渡解析は AC 解析と違い非線形領域もカバーしているのでサチレーションの観測も可能である。

横軸が時間のグラフとなり、オシロスコープによる観測になる。

このほかに温度変化の影響を調べるシミュレーション、素子の値のばらつき による影響を調べるシミュレーション等も行える。

### 3.4 設計例

- カウントダウン時計 -

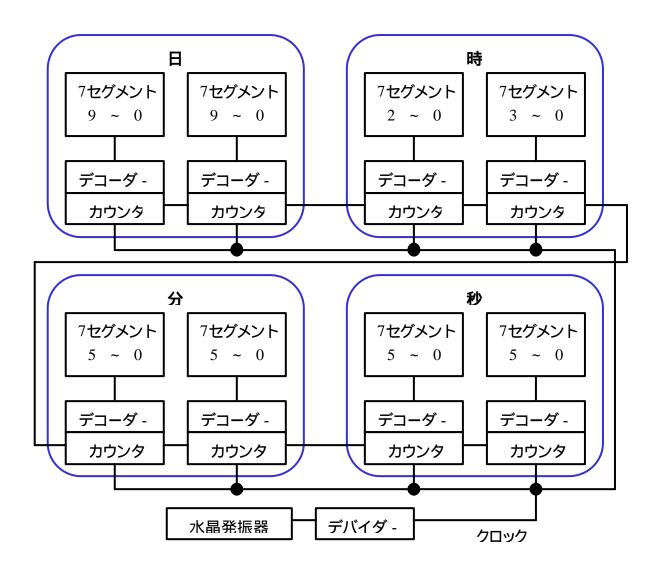

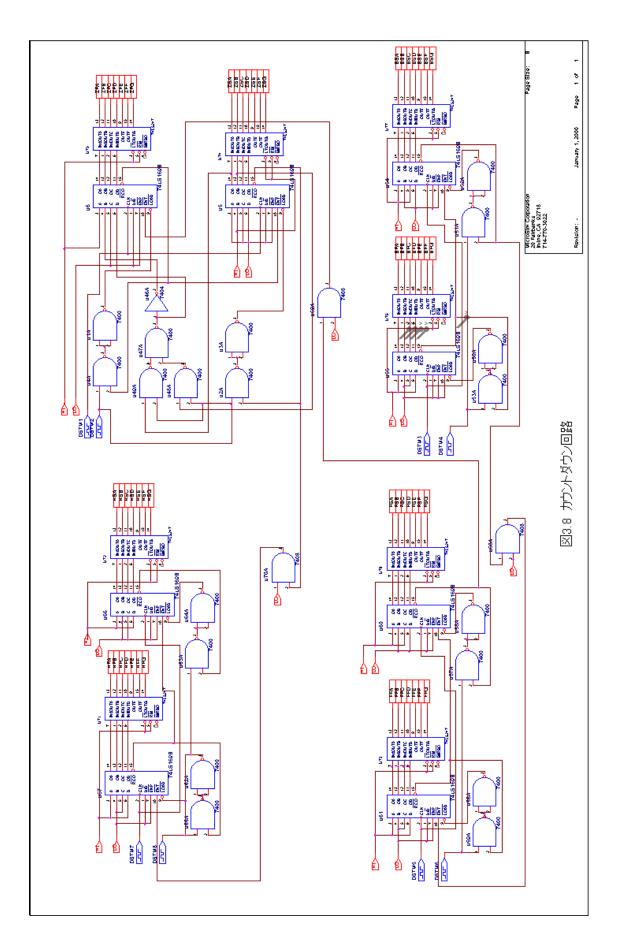

今回は水晶発振器から発振された信号をデバイダ - に通すことによって 1Hz のクロックを生成し、S N 74 L S 169 B を用いてカウントし 7 セグメントにて表示させるカウントダウン回路を設計した。この回路は最大 99 日 23 時間 59 分59秒までカウントダウンすることができる。全体のブロック図を図 3.2 に示す。

図 3.2 カウントダウン時計のブロック図

## 今回使用した主な材料

- ・抵抗

- 10K スイッチ用 4本

- 220 セグメント用 56本

- · IC

- SN74LS247P セグメント用 8 個

- 4 ビットの信号を 7 ビットの信号に変換するために使用した。

- SN74LS169BN カウントダウン用 8 個

- SN74LS08N AND 回路用 4個

- SN74LS00N NAND 回路用 1個

SN74LS292N プログラマブルデバイダ 1 個 クロックを FF に何回通過させるかを外部から設定できる。クロックの 周波数を 1 Hz にまで落とすために使用した。

・ 水晶 (TOYOCOM TCO - 707F 4.194304MHz)

FF を通過するたびに周波数が 2 分の 1 される。このため周波数は 2  $^{\mathsf{n}}$

である必要があり、そこで 4.194304MHz ( $2^{22}$  Hz) を使用した。

- ・ セグメント 8個

- ・ 電解コンデンサ (470 µF) 電源用 2個

- · セラミックコンデンサ(0.1 µF)スイッチ用 4個

- ・ プッシュスイッチ 4個

カウントダウン時計の製作に用いるそれぞれの標準論理ICの動作特性と回路 構成を以下に表や図としてまとめる。

## SN74LS00 \(\sum\_SN74LS08\)

SN74LS00 は NAND 回路の IC であり、SN74LS08 は AND 回路の IC である。

表 3.7 SN74LS00 と SN74LS08 の動作特性

|                               | SN74LS00 |     | SN74LS08 |      |     |      |

|-------------------------------|----------|-----|----------|------|-----|------|

|                               | MIN      | NOM | MAX      | MIN  | NOM | MAX  |

| Vcc Suppy voltage (V)         | 4.75     | 5   | 5.25     | 4.75 | 5   | 5.25 |

| Vін High-level input voltage  | 2        |     |          | 2    |     |      |

| (V)                           |          |     |          |      |     |      |

| Vп. Low-level input voltage   |          |     | 0.8      |      |     | 0.8  |

| (V)                           |          |     |          |      |     |      |

| Iон High-level output current |          |     | -0.4     |      |     | -0.8 |

| (mA)                          |          |     |          |      |     |      |

| Iol Low-level output current  |          |     | 16       |      |     | 16   |

| (mA)                          |          |     |          |      |     |      |

| TA Operating free-air         | 0        |     | 70       | 0    |     | 70   |

| temperature ( )               |          |     |          |      |     |      |

図 3.3 N74LS00 と SN74LS08 の IC のピン配置図

表 3.8 SN74LS00 と SN74LS08 の状態表

| SN74LS00 |            |   |  |  |  |  |

|----------|------------|---|--|--|--|--|

| 入        | 入力 出力      |   |  |  |  |  |

| A        |            |   |  |  |  |  |

| L        | L L<br>L H |   |  |  |  |  |

| L        |            |   |  |  |  |  |

| Н        | L          | L |  |  |  |  |

| Н        | Н Н        |   |  |  |  |  |

| SN74LS08 |    |   |  |  |  |  |  |

|----------|----|---|--|--|--|--|--|

| 入        | 入力 |   |  |  |  |  |  |

| A        | В  | Y |  |  |  |  |  |

| L        | L  | Н |  |  |  |  |  |

| L        | Н  | L |  |  |  |  |  |

| Н        | L  | L |  |  |  |  |  |

| Н        | Н  | L |  |  |  |  |  |

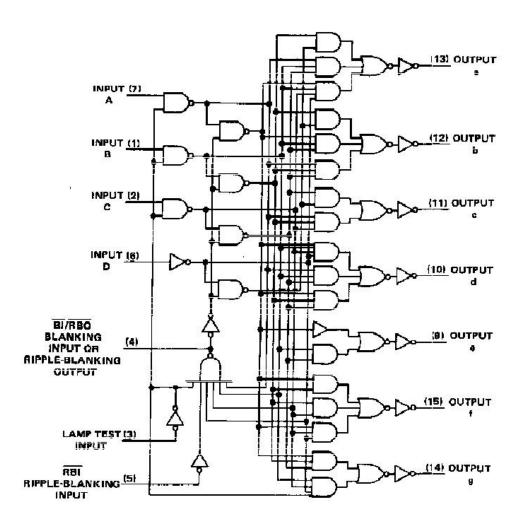

## SN74LS169B

SN74LS169B は同期式 4 ビット アップ/ダウン バイナリーカウンタの IC である。

表 3.9 74LS169B の動作特性

|                                | SN                                           | N74LS16 | 9B  |      |

|--------------------------------|----------------------------------------------|---------|-----|------|

|                                | MIN                                          | NOM     | MAX |      |

| VCC Suppy voltage              | 4.5                                          | 5       | 5.5 |      |

| VIH High-level input vol       | ltage (V)                                    | 2       |     |      |

| VIL Low-level input volt       | age (V)                                      |         |     | 0.8  |

| IOH High-level output cur      | rent (mA)                                    |         |     | -0.4 |

| IOL Low-level output curr      | rent (mA)                                    |         |     | 8    |

| Fclock Clock frequency         | (MHz)                                        | 0       |     | 40   |

| tw Pulse duration, CLK high of | or Low (ns)                                  | 12.5    |     |      |

|                                | A, S, C or D                                 | 15      |     |      |

| tsu Setup time sefore CLK (ns) | $\overline{\it ENP}$ or $\overline{\it ENT}$ | 15      |     |      |

|                                | $\overline{LOAD}$                            | 15      |     |      |

|                                | $U/\overline{D}$                             | 15      |     |      |

| th Hold time,data after        | 0                                            |         |     |      |

| TA Operating free-air tempo    | erature ( )                                  | 0       |     | 70   |

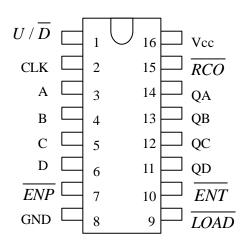

SN74LS169B はカウントをアップするかダウンさせるか選択することができる。カウントアップしたい場合は、下の図 3.4 ピン番号 1 番に H レベルの信号を入れる。逆にカウントダウンしたい場合は、L レベルの信号を入れる。今回はカウントダウンする回路を製作するのでピン番号 1 番に L レベルの信号を入れた。

図 3.4 74LS169B の IC のピン配置図

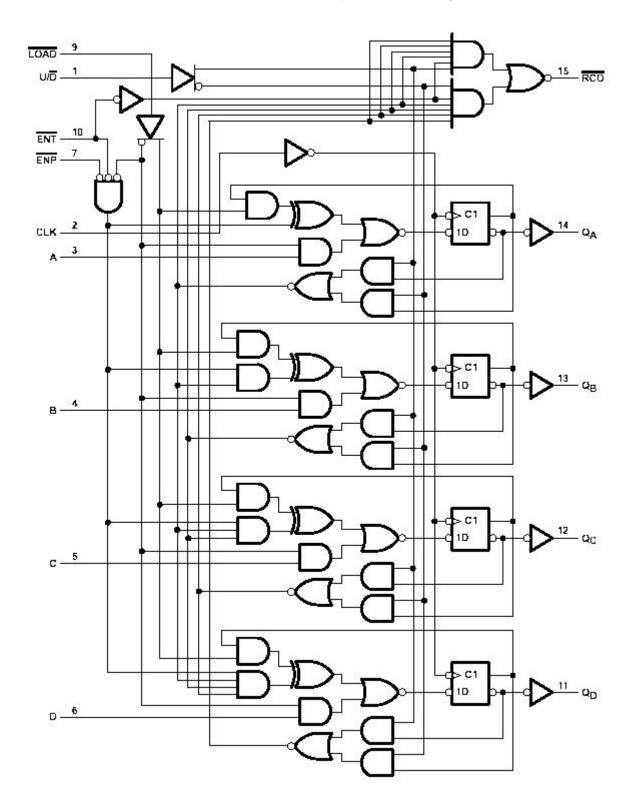

SN74LS169B を論理回路で表すと図 3.5 のようになっている。

図 3.5 N74LS169B の論理回路図

(参考: http://www.tij.co.jp)

SN74LS169B は $\overline{ENP}$  と $\overline{ENT}$  の AND を取った信号が L レベルの時にだけ動作する。 $\overline{RCO}$  は次の桁に桁上げないし、桁下げの信号を出力する。 $\overline{LOAD}$  はカウントアップ/ダウン時にクロックに同期して信号を割り込ませてカウントを 1 つ先に進めることができる。

## **SN74LS292N**

SN74LS292N はプログラマブルデバイダであり、水晶発振器からクロックをこの IC に通して 1Hz にする。

表 3.10 SN74LS292N の動作特性

|                                         | SN74LS292N |     |      |

|-----------------------------------------|------------|-----|------|

|                                         | MIN        | NOM | MAX  |

| Vcc Suppy voltage (V)                   | 4.7        | 5   | 5.25 |

| VIH High-level input voltage (V)        | 2          |     |      |

| VIL Low-level input voltage (V)         |            |     | 0.8  |

| Iон High-level output current           |            |     | -1.2 |

| (mA)                                    |            |     |      |

| Iol Low-level output current (mA)       |            |     | 24   |

| Fclock Clock frequency (MHz)            | 0          |     | 30   |

| tw Pulse duration, CLK high or Low (ns) | 16         |     |      |

| tsu Setup time sefore CLK (ns)          | 55         |     |      |

| th Hold time,data after CLK             | 15         |     |      |

| TA Operating free-air temperature       |            |     |      |

| ( )                                     | 0          |     | 70   |

## SN74LS247P

SN74LS247P はデコーダーであり、SN74LS169B から出力された 4 ビットの BCD コードの出力を 8 ビットにデコードし 7 セグメントへ出力する。

表 3.11 SN74LS247P の動作特性

|                               | SN74LS247P                         |      |   |      |  |

|-------------------------------|------------------------------------|------|---|------|--|

|                               |                                    |      |   |      |  |

| Vcc Suppy voltage (V          | )                                  | 4.75 | 5 | 5.25 |  |

| Vo Off-state output voltage   | a thru g                           |      |   | 15   |  |

| Io On-state output current    | a thru g                           |      |   | 40   |  |

| Ioн High-level output current |                                    |      |   | -200 |  |

| ( µ A)                        | $\overline{BI}$ / $\overline{RBO}$ |      |   |      |  |

| Iol Low-level output current  |                                    |      |   | 8    |  |

| (mA)                          | $\overline{BI}$ / $\overline{RBO}$ |      |   |      |  |

| TA Operating free-air tempera | ature ( )                          | 0    |   | 70   |  |

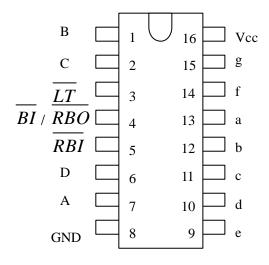

図 3.6 SN74LS247P のピン配置図

SN74LS247P は $\overline{BI}$  /  $\overline{RBO}$  が H レベルのとき動作する。LT、RBI が H レベルのとき入力をデコードし出力する。どちらかが L レベルになると出力が全て L レベル ( OFF 状態 ) になる。

表 3.12 SN74LS247P の状態表

| 入力 |   |   |   |   |   |   | 出力 |   |   |   |

|----|---|---|---|---|---|---|----|---|---|---|

| A  | В | C | D | a | b | С | d  | e | f | g |

| 0  | 0 | 0 | 0 | 1 | 1 | 1 | 1  | 1 | 1 | 0 |

| 0  | 0 | 0 | 1 | 0 | 1 | 1 | 0  | 0 | 0 | 0 |

| 0  | 0 | 1 | 0 | 1 | 1 | 0 | 1  | 1 | 0 | 1 |

| 0  | 0 | 1 | 1 | 1 | 1 | 1 | 1  | 0 | 0 | 1 |

| 0  | 1 | 0 | 0 | 0 | 1 | 1 | 0  | 0 | 1 | 1 |

| 0  | 1 | 0 | 1 | 1 | 0 | 1 | 1  | 0 | 1 | 1 |

| 0  | 1 | 1 | 0 | 1 | 0 | 1 | 1  | 1 | 1 | 1 |

| 0  | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 0 | 0 | 0 |

| 1  | 0 | 0 | 0 | 1 | 1 | 1 | 1  | 1 | 1 | 1 |

| 1  | 0 | 0 | 1 | 1 | 1 | 1 | 1  | 0 | 1 | 1 |

図 3.7 SN74LS247P の論理回路図

(参考: http://www.tij.co.jp)

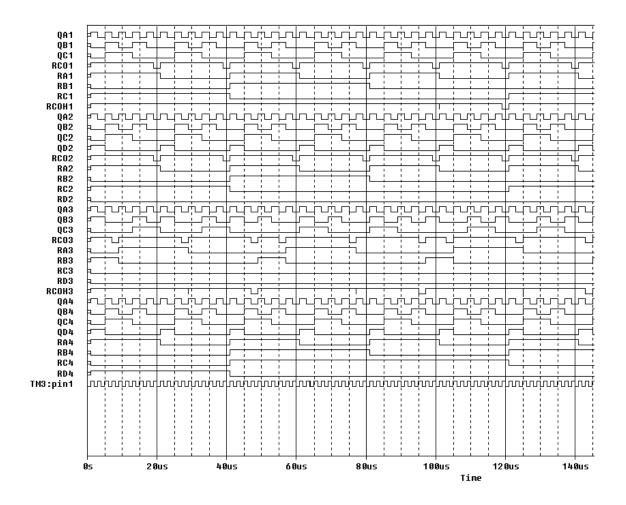

Orcad の Capture で実際に組み上げた回路が図 3.8 であり、PSpice でシミュレーションのため桁上げ信号をカットし、日、時間、分、秒が同時に作動するようにしている。これを PSpice A/D でシミュレーションした結果が図 3.9 である。

図 3.9 シミュレーション結果

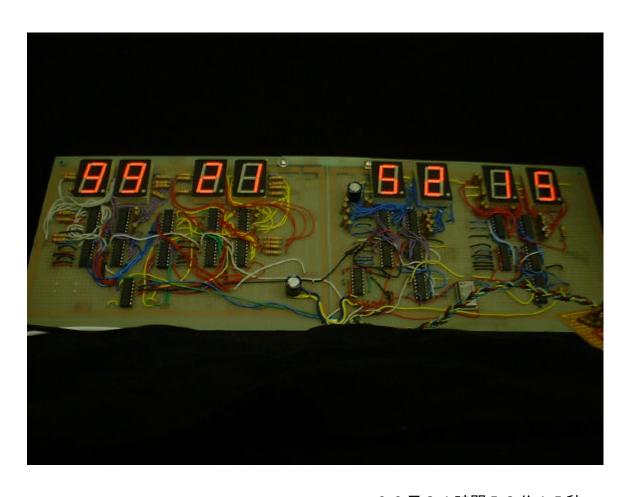

## 完成図

出来上がった回路を実際に形にしてみようということで、市販のプリント基盤の上にさまざまな部品を組み上げてみた。この図 3.10 は実際に出来上がりカウントダウンしている様子をデジタルカメラにて撮影したところである。

99日21時間52分15秒 図3.10 カウントダウン時計

# 第4章 ハードウェア記述言語による 回路設計

## 4.1 ハードウェア記述言語

ハードウェア記述言語(HDL: Hardware Description Language)とは、今まで人間の手作業によるディジタル回路の設計作業が、半導体集積化技術の飛躍的な向上に伴い、設計するディジタル・システムの規模は増大したため人間の手作業による回路図作成では限界となり開発された、Cや Pascal などのような形式言語である。ただしプログラム言語とは異なり、ハードウェアを設計するうえで欠かせない並列処理(同時処理)や時間、タイミングの概念などを記述できるものである。

HDLが出現したことによって、VLSI設計の手法は大きく変わってきた。 従来はRTL 1(Register Transfer Level)回路の記述は仕様書をもとに行われており、計算機で動作を検証できるRTL表現も存在したが、ゲートレベルへの展開が可能な表現はなかったので、人間の手作業で回路を構築してゆくボトムアップ的設計手法 2がとられてきた。1980年代後半になって、VHDLやVerilog HDLといったハードウェア記述言語が開発されてRTL回路はHDLで記述する事が一般的になり、ゲートレベルへの展開が可能になってきた。このように、HDLを用いてRTL設計をすることをHDL設計と呼んでいる。表1に今までに開発された主なHDLをまとめてみた。

#### 1RTL

仕様設計から出力された仕様書をもとに、まずLSI内部を機能ブロックに分割し、さらにブロックがレジスタと組合せ回路とで構成されるところまでブロック分割を繰り返す。そのようにして得られたブロックの中のレジスタとレジスタの間の組合せ回路を決定したうえで、クロックごとの回路動作を決定する。このときの表現をRTL記述といい、抽象度をRTLという。RTL設計は機能設計とも呼ぶ。

### 2ボトムアップ設計

まず開発対象となるディジタル回路をいくつかのブロックに分割し、設計された各ブロックを組み合わせて回路全体を構成する方法のこと。過去の設計資産を再利用しやすいので、大規模なディジタル回路の設計において採用されてきた。

表 1 HDL の歴史

| 言語       | VHDL   | Verilog HDL | UDL/I     | SFL     |

|----------|--------|-------------|-----------|---------|

| 開発開始時期   | 1981年  | 1984 年      | 1987年     | 1981年   |

| 開発組織     | IEEE   | Cadence     | 日本電子工業振興会 | NTT     |

| 言語仕様公表   | 1987年  | 1985 年      | 1990年     | 1985 年  |

| 論理シミュレータ | 有      | 有           | 有         | SECONDS |

| 論理合成系    | 有      | 有           | 有         | SFLEXP  |

| 規格の見直し   | 1993 年 | 1999年(予定)   | 1992 年    | 予定なし    |

この表で、VHDL(Very High Speed integrated circuit Hardware Description Language)は1981年にスタートした米国国防総省のVHSIC(Very High Speed IC)プロジェクトで開発されたHDLであり、1987年末にIEEE Std 1076として、1993年にはIEEE Std 1164として規格が正式に承認され世界的に標準化された。VHDLはシステムからスイッチにいたるハードウェア全般の記述を対象としており、ハードウェアの構造と動作の両方を記述できる。VHDLでは回路を階層的にとらえ、ある回路は下位のより小さな回路が接続されたものとして記述する。最下層の回路を動作的に記述し、それより上位の回路を構造的に記述する。VHDLは、ユーザ定義のタイプ、抽象度の高いデータタイプ、回路構成をコントロールするためのコンフィギュレーションなどに特徴がある。

また、Verilog HDL は米国の Cadence 社で Verilog XL というシミュレータ用に開発された HDL であり、世界的に普及している。しかし、標準化されたのは以外に遅く、1995 年に IEEE Std 1364 となった。Verilog HDL はシステムからスイッチにいたるハードウェア全般の記述を対象としており、ハードウェアの構造と動作の両方を記述できる。Verilog HDL でも回路は階層的に記述する。再下位層の回路は動作的に記述し、上位の回路は構造的に記述する。特徴として RTL に的を絞った簡素な記述で、テストパターン記述言語としての高い効率性などがあげられる。

SFL は日本で開発された HDL であり、制御回路の記述に特徴がある。SFL では、回路をデータパス部と制御回路に明示的に分けて記述し、制御回路の記述中からデータパスを構成する部品を手続き的に呼び出すことにより回路の動作を記述する。データパスを構成する部品間の接続やデータパスと制御回路の間の接続は合成によって行われる。制御回路の記述は単一クロックの完全同期

式ステートマシンを基本としている。SFL では階層的なステートマシンの表現が可能であり、複数のステートマシンによる並列処理、パイプライン処理、置いてきぼり処理の記述が可能である。SFL は複雑な回路を簡単に記述できる点で VHDL や Verilog HDL より優れているがあまり普及していない。なぜならSFL の回路設計思想であるデータパスと制御回路を完全に分離して設計するスタイルが一般に理解されにくく、また日本で開発されたため外国では知名度も低くツールなどのサポートが弱いためである。

このように何種類ものHDLが開発されていますが、今回は現在広く普及しているVHDLを用いることにした。

## 4.2 **VHDLによる記述方法**

実際にはどのように使われているか、JK-FFのVHDLの記述を参考例として示す。

```

library IEEE;

2

use IEEE.std_logic_1164.all;

3

4

entity JK_FF is

5

port (CK, J, K : in std_logic;

6

Q, Qnot: out std_logic);

7

end JK FF;

8

9

architecture BEHAVIOR of JK FF is

10

11 signal INPUT : std_logic_vector ( 2 downto 0)

12 signal TMP : std_logic;

13

14 begin

15

INPUT <= CK & J & K;

16

process (INPUT) begin

17

case INPUT is

when "101" => TMP <= '0';

18

19

when "110" => TMP <= '1';

20

when "111" => TMP <= not TMP;

21

when others => null:

```

- 22 end case:

- 23 end process;

- Q < TMP;

- 25 Qnot  $\leq$  not TMP;

- 26 end BEHAVIOR:

### ○データタイプ

VHDLには、論理型のデータ・タイプとして、論理値 '0' または、'1' しかとれない bit 型およびその配列タイプである bit\_vector 型しかなかった。しかし、ディジタル回路の設計やシミュレーション、論理合成などを行う際には、不定値 'X'、ハイ・インピーダンス 'Z'、ドント・ケア '-' などを使用できることが望ましい。

## 1~2行目

IEEE=The Institute of Electrical and Electronics Engineers 米国電気電子技術者協会

○エンティティとアーキテクチャ

ディジタル回路は、それに入力された何らかの信号(データ)に加工を施し、 その加工結果を出力する電子回路である。このようなディジタル回路を設計す るためには、

どのような信号が入力されるか?

その信号にどのような加工を施すのか?

どのような信号を出力させるのか?

を明確にする必要がある。

や の情報は、外部から入力される信号(入力信号)や外部へ出力する信号(出力信号)に関する情報、すなわち、インターフェースに関する情報である。これに対して の情報は、回路内部の動作や構造に関する情報である。VHDLでは、これらの外部情報が、エンティティ(entity)4から7行目、内部情報がアーキテクチャ(architecture)9~26行目と呼ぶ。

#### ○信号線

それが入力信号線(入力ポート)なのか、(出力ポート)なのか、あるいは入出力 兼用なのかを定める必要がある。

### ○信号の代入と演算子

ディジタル回路の動作や構造を記述する。データの流れを記述するためには、 信号代入文 < = を用いる。信号代入文では、複数の信号間には論理演算などを 施し、その結果を他の信号線に代入することもできる。15.18~21.24.25 行目

## 4.3 VHDL による順序回路の設計例 カウントダウン時計

VHDLによる順序回路の設計として、実際に Electronics Workbench の multiSIM VHDL を用いてカウントダウン時計を設計した。このカウントダウン時計は10進カウンタ部、7セグメントディスプレイ表示部、日、時間、分、 秒の設定部から構成されている。以下に各部の設計について説明する。

## 4.3.1 7 セグメントディスプレイ表示部

```

Library ieee;

use ieee.std_logic_1164.all;

entity segment7 is

port (

DI : in std logic vector(3 downto 0);

DO : out std_logic_vector(6 downto 0)

);

end segment7;

architecture RTL of segment7 is

begin

process(DI)

begin

case DI is

--qfedcba

when "0000" => DO <= "0111111";

when "0001" => DO <= "0000110";

when "0010" => DO <= "1011011";

when "0011" => DO <= "1001111";

when "0100" => DO <= "1100110";

when "0101" => DO <= "1111101";

when "0111" => DO <= "0000111";

when "1000" => DO <= "11111111";

when "1001" => DO <= "1101111";

when others => DO <= "11111111";

end case;

end process;

end RTL;

```

4.3.1の記述は実際にカウントされた数値が出力として表示される部分の設定であり、4ビットのデータから7ビットのデータへの変換や端子の入出力の設定をしている。

## 4.3.2 10進力ウンタ部

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic unsigned.all;

entity count10 is

port (

CLK,RESET : in std_logic;

CYin

: in std logic;

: out std_logic_vector ( 3 downto 0 );

Q

CYout : out std_logic

);

end count10;

architecture RTL of count10 is

signal TQ : std_logic_vector ( 3 downto 0 );

begin

process ( CLK, RESET, CYin ) begin --10count

if ( RESET = '1' ) then

TO <= "0000";

elsif ( CLK 'event and CLK = '1' and CYin ='1' ) then

if (TQ = "0000") then

TO <= "1001";

else

TQ <= TQ - '1';

end if;

end if;

end process;

process ( TQ,CYin ) begin

if (TQ = "0000" and CYin = '1') then

CYout <= '1';

```

4.3.2の記述は、10進数のカウンタの設定で9からカウントダウンして0になるとまた9に戻ると言う命令を記述している。またデータと端子の入出力の設定も行っている。

## 4.3.3 日、時間、分、秒の設定部

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CDT is

port ( CLK, RESET

: in std_logic;

SBF, SBS : out std_logic_vector(6 downto 0);

--byou

: out std_logic_vector(6 downto 0); --hun

SHF, SHS

SJF, SJS : out std_logic_vector(6 downto

0);--jikan

SHIF, SHIS : out std_logic_vector(6 downto 0)

--hiniti

);

end CDT;

architecture RTL of CDT is

component segment7

port (

DI : in std_logic_vector(3 downto 0);

DO : out std_logic_vector(6 downto 0)

```

```

);

end component;

component COUNT10 is

port (

: in std_logic;

CLK, RESET

CYin

: in std_logic;

: out std_logic_vector(3 downto 0);

0

: out std_logic

CYout

);

end component;

signal TQi, TQj, TQk, TQl, TQm, TQn, TQo, TQp

: std_logic_vector(3 downto 0);

signal CYa, CYb, CYc, CYd, CYe, CYf, CYg : std_logic;

begin

--byou

process (CLK, RESET) begin

if (RESET = '1' ) then

TOi <= "1001";

elsif (CLK'event and CLK = '1' ) then

if (TQi = "0000") then

TQi <= "1001";

else

TOi <= TOi - '1';

end if;

end if;

end process;

process (TQi) begin

if (TQi = "0000") then

CYa <= '1';

else

CYa <= '0';

```

```

end if;

end process;

process (CLK, RESET, CYa) begin

if (RESET = '1' ) then

TQj <= "0101";

elsif (CLK'event and CLK = '1' and CYa ='1') then

if (TQj = "0000") then

TQj <= "0101";

else

TQj <= TQj - '1';

end if;

end if;

end process;

process (TQj,CYa) begin

if (TQj = "0000" and CYa = '1') then

CYb <= '1';

else

CYb <= '0';

end if;

end process;

--hun

process (CLK, RESET, CYb) begin

if (RESET = '1' ) then

TOk <= "1001";

elsif (CLK'event and CLK = '1' and CYb = '1' ) then

if (TQk = "0000") then

TOk <= "1001";

else

TQk \leftarrow TQk - '1';

end if;

end if;

end process;

```

```

process (TQk, CYb) begin

if (TQk = "0000" and CYb = '1') then

CYc <= '1';

else

CYc <= '0';

end if;

end process;

process (CLK, RESET, CYc) begin

if (RESET = '1' ) then

TQ1 <= "0101";

elsif (CLK'event and CLK = '1' and CYc ='1') then

if (TQl = "0000") then

TQ1 <= "0101";

else

TQ1 <= TQ1 - '1';

end if;

end if;

end process;

process (TQl,CYc) begin

if (TOl = "0000" and CYc = '1') then

CYd <= '1';

else

CYd <= '0';

end if;

end process;

--jikan

process (CLK, RESET, CYd) begin

if (RESET = '1' ) then

TOm <= "0011";

elsif (CLK'event and CLK = '1' and CYd = '1') then

if (TQm = "0000") then

TOm <= "1001";

if (TQm = "0000" and TQn = "0000") then

```

```

TQm <= "0011";

end if; -- <= point

else

TQm <= TQm - '1';

end if;

end if;

end process;

process (TQm, CYd) begin

if (TQm = "0000" and CYd = '1') then

CYe <= '1';

else

CYe <= '0';

end if;

end process;

process (CLK, RESET, CYe) begin

if (RESET = '1' ) then

TQn <= "0010";

elsif (CLK'event and CLK = '1' and CYe ='1') then

if (TOn = "0000") then

TQn <= "0010";

else

TQn <= TQn - '1';

end if;

end if;

end process;

process (TQn,CYe) begin

if (TQn = "0000" and CYe = '1') then

CYf <= '1';

else

CYf <= '0';

end if;

end process;

```

```

--hiniti

process (CLK, RESET) begin

if (RESET = '1' ) then

TQo <= "1001";

elsif (CLK'event and CLK = '1' and CYf = '1') then

if (TQo = "0000") then

TOo <= "1001";

else

TQo <= TQo - '1';

end if;

end if;

end process;

process (TQi, CYf) begin

if (TOi = "0000" and CYf = '1') then

CYg <= '1';

else

CYg <= '0';

end if;

end process;

process (CLK, RESET, CYg) begin

if (RESET = '1' ) then

TQp <= "1001";

elsif (CLK'event and CLK = '1' and CYg ='1') then

if (TQp = "0000") then

TQp <= "1001";

else

TQp <= TQp - '1';

end if;

end if;

end process;

--7seg

UO : segment7 port map(TQi, SBF);--byou

```

```

U1 : segment7 port map(TQj, SBS);

U2 : segment7 port map(TQk, SHF);--hun

U3 : segment7 port map(TQl, SHS);

U4 : segment7 port map(TQm, SJF);--jikan

U5 : segment7 port map(TQn, SJS);

U6 : segment7 port map(TQo, SHIF);--hiniti

U7 : segment7 port map(TQp, SHIS);

```

4.3.3 の記述は実際のカウントダウン時計の内部設定をしている。日の部分は99から0まで、時間の設定は23から0までのカウントダウンである。分、秒は59から0までのカウントダウンとなっている。これら全てを10進カウンタのみで書き上げている。また、データと端子の入出力の設定をし、7セグメント部や10進カウンタ部への接続も記述している。

# 4.3.4 7 セグメントディスプレイのテストベンチ記述

```

architecture stimulus of TESTBNCH is

component SEGMENT7 is

port (

DI : in std_logic_vector (3 downto 0);

DO : out std_logic_vector (6 downto 0)

);

end component;

constant PERIOD: time := 100 ns;

signal DI : std_logic_vector (3 downto 0);

signal D0 : std_logic_vector (6 downto 0);

begin

DUT: SEGMENT7 port map (

DI,

DO

);

process

begin

DI <= "0000"; wait for 75 ns;

DI <= "0001"; wait for 75 ns;

DI <= "0010"; wait for 75 ns;

DI <= "0011"; wait for 75 ns;

DI <= "0100"; wait for 75 ns;

DI <= "0101"; wait for 75 ns;

DI <= "0110"; wait for 75 ns;

DI <= "0111"; wait for 75 ns;

DI <= "1000"; wait for 75 ns;

DI <= "1001"; wait for 75 ns;

DI <= "0000"; wait for 75 ns;

```

```

wait ;

end process;

end stimulus;

```

4.3.4 の記述は7 セグメントディスプレイの設定をシミュレーションするため にテストベンチ記述したものである。

## 4.3.5 10 進カウンタのテストベンチ記述

```

-- Auto-generated test bench template for: COUNT10

-- Note: comments beginning with WIZ should be left intact.

Other comments are informational only.

-- Multisim VHDL software version: 5.15a

library ieee;

use ieee.std_logic_1164.all;

-- use ieee.numeric_std.all; -- Note: uncomment this if you

use

-- IEEE standard signed or

unsigned types.

-- use ieee.std_logic_arith.all; -- Note: uncomment/modify

this if you use

-- Synopsys signed or unsigned

types.

use std.textio.all;

use work.COUNT10;

entity TESTBNCH is

end TESTBNCH;

architecture stimulus of TESTBNCH is

component COUNT10 is

port (

```

```

clk: in std_logic;

reset: in std_logic;

CYin: in std_logic;

Q: out std_logic_vector(3 downto 0);

CYout: out std_logic

);

end component;

-- Top level signals go here...

signal clk: std_logic;

signal reset: std_logic;

signal CYin: std_logic;

signal Q: std_logic_vector(3 downto 0);

signal CYout: std_logic;

signal clock_cycle : natural :=0;

begin

DUT: COUNT10 port map (

clk,

reset,

CYin,

Ο,

CYout

);

CLOCK1: process

begin

clock_cycle <= clock_cycle + 1;</pre>

clk <= '1'; wait for 30ns;</pre>

clk <= '0'; wait for 30ns;

end process CLOCK1;

STIMULUS1: process

begin

-- Sequential stimulus goes here...

```

```

--

-- Sample stimulus...

RESET <= '1'; -- Reset the system

wait for 30ns; -- Wait one clock cycle

RESET <= '0'; -- de-assert reset

--

-- Enter more stimulus here...

--

CYin <= '1';

wait; -- Suspend simulation

end process STIMULUS1;

end stimulus;

```

4.3.5 の記述は 10 進力ウンタの設定をシミュレーションするためにテストベンチ記述したものである。

# 4.3.6 日、時間、分、秒の設定のテストベンチ記述

```

architecture stimulus of TESTBNCH is

component CDT is

port (

CLK: in std_logic;

Reset: in std_logic;

SBF: out std_logic_vector(6 downto 0);

SBS: out std logic vector(6 downto 0);

SHF: out std_logic_vector(6 downto 0);

SHS: out std_logic_vector(6 downto 0);

SJF: out std_logic_vector(6 downto 0);

SJS: out std_logic_vector(6 downto 0);

SHIF: out std_logic_vector(6 downto 0);

SHIS: out std_logic_vector(6 downto 0)

);

end component;

-- Top level signals go here...

signal CLK: std logic;

signal Reset: std_logic;

signal SBF: std_logic_vector(6 downto 0);

signal SBS: std logic vector(6 downto 0);

signal SHF: std_logic_vector(6 downto 0);

signal SHS: std_logic_vector(6 downto 0);

signal SJF: std_logic_vector(6 downto 0);

signal SJS: std_logic_vector(6 downto 0);

signal SHIF: std_logic_vector(6 downto 0);

signal SHIS: std_logic_vector(6 downto 0);

signal Clock_cycle: std_logic;

begin

DUT: CDT port map (

CLK,

Reset,

SBF,

SBS,

```

```

SHF,

SHS,

SJF,

SJS,

SHIF,

SHIS

);

CLOCK1: process

begin

Clock_cycle <= Clock_cycle + '1';</pre>

CLK <= '1'; wait for 10ns;

CLK <= '0'; wait for 10ns;

end process CLOCK1;

STIMULUS1: process

begin

RESET <= '1'; wait for 15ns;</pre>

RESET <= '0';

wait;

-- Suspend simulation

end process STIMULUS1;

end stimulus;

```

4.3.6 の記述は、日、時間、分、秒の設定をシミュレーションするためにテストベンチ記述したものである。

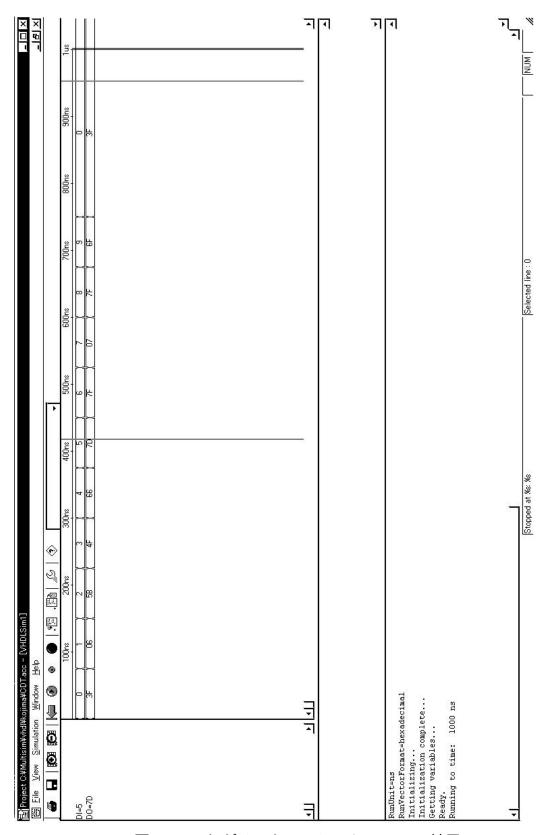

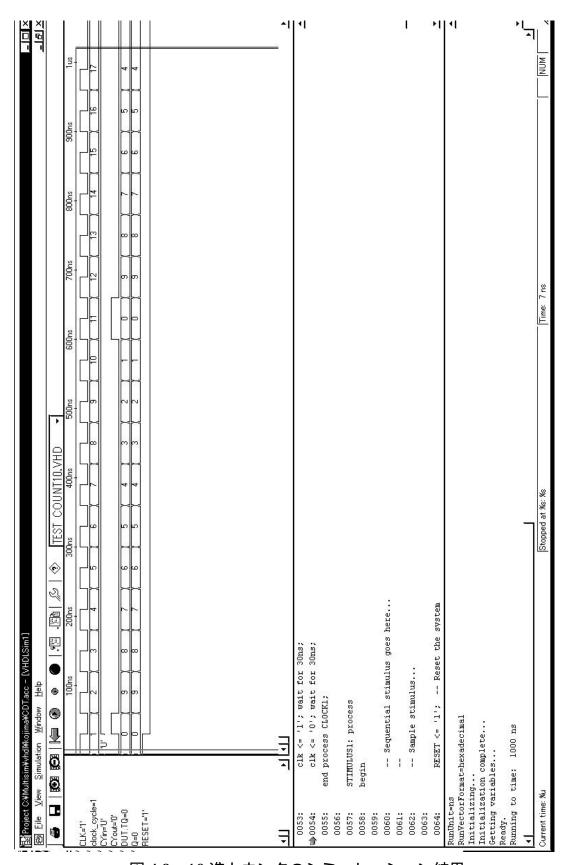

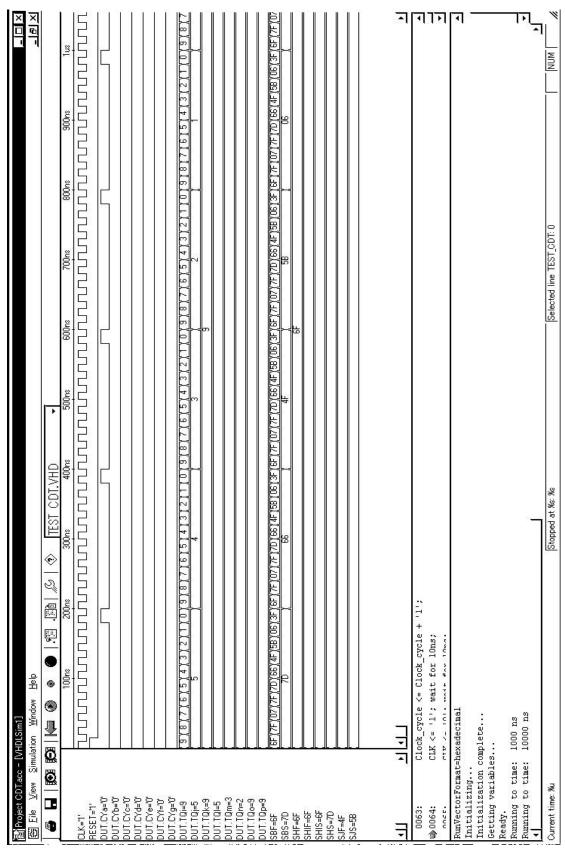

これらのテストベンチを実際にシミュレーションした結果をそれぞれ 7 セグメントが図 4.1、 1 0 進カウンタが図 4.2、日、時間、分、秒の設定が図 4.3 となる。シミュレーションするにあたり、出力される波形を見るのが目的であるため、短時間でより多くの表示させるように  $1\sec = 10$ ns、15ns、30ns、75ns として使っている

図 4.1 7 セグメントのシミュレーション結果

図 4.2 10 進力ウンタのシミュレーション結果

図 4.3 日、時間、分、秒の設定のシミュレーション結果の一部

# 第5章 おわりに

今回の課題を取り組んだことによって、最初の目的通りディジタル回路の基本である順序回路について、かなり理解することができた。特に最初は難しいと思われた順序回路設計も、実際に一通り体験して見ることで実際の雰囲気が少しつかめた。実際には本当に基本的なことしかできていないが、VHDL、PSpice と言う代表的な回路設計の方法を使うことによって、何とか回路設計ができるようになった。

### 今後の課題

今回の実験を終えてみて、反省点がいくつかある。

- ・ 限られた時間にもかかわらず、予定をたてそれをこなしていくと言うスケジュール管理がしっかりとできなかった点。

- ・ どの項目についても中途半端な理解で、完全にマスターし使いこなせるレベルまで到達できなかった点。

これらの反省点は今回の実験だけに限らず、今後社会にでても必要とされることなので、しっかりと反省し今後の機会に生かしていきたいと思う。

# 謝辞

本研究を行うに際し、終始、懇切丁寧な御指導、御鞭撻を賜わりました。 高知工科大学 電子・光システム工学科 矢野政顯 教授に心から感謝いた します。

研究中、懇切丁寧なご指導を賜わりました高知工科大学 電子・光システム工学科学科長 原央 教授、高知工科大学 電子・光システム工学科 河津哲 教授、高知工科大学 電子・光システム工学科 橘昌良 助教授に厚くお礼申し上げます。

また終始、適切な御助言、御助力をいただきました高知工科大学 電子・光システム工学科専攻 北野克幸氏、小泉義信氏、田口禎譲氏、中村基継氏ほか計算機応用講座の矢野研究室はじめ隣の原研究室、河津研究室、橘研究室の皆様に心から感謝お礼申し上げます。

# 参考文献

笹尾 勤 著 "論理設計 スイッチング回路理論" 近代科学社 柴山 潔 著 "コンピュータアーキテクチャの基礎" 近代科学社 浜辺 隆二 著 "論理回路入門" 森北出版株式会社 高橋 寛・関根好文・作田幸憲/著 "ディジタル回路" コロナ社 深山正幸・北川章夫・秋田純一・鈴木正國/著 "HDL による VLSI 設計"共立出版株式会社 吉田たけお・尾知 博/著 "入門!VHDL による回路設計の基礎"

Design Wave Magazine 2000 年 12 月号特集より