# 卒業研究報告

題 目

MOSトランジスタの基本特性

指 導 教 員

原 央 教授

報 告 者

藤川 宏隆

平成 13年 2月 9日

高知工科大学 電子・光システム工学科

# 目次

- 1.目的

- 2. 方法

- 3.MOSトランジスタの基本特性

- 3 1 . ドレイン電流特性

- 3 1 1 . 簡単なドレイン電流特性

- 3 2 . しきい値電圧

- 3 2 1 . フラットバンド電圧

- 3 2 2 . しきい値電圧

- 3-3.擬フェルミレベル

- 3 4 . 基板バイアス効果

- 4.移動度

- 4-1.移動度とは

- 4-2.MOSトランジスタの移動度

- 5. MOSトランジスタの測定

- 5 1 . 実験器具

- 5 2 . 測定したMOSトランジスタ

- 5 3 . 実験方法

- 5 4 . 実験結果(データ)

- 5 4 1 . ドレイン電流特性

- 5 4 2 . 移動度

- 5 4 3 . 基板バイアス効果

- (1) 基板バイアスにおけるしきい値の変化

- (2) 基板バイアス効果による移動度の変化

- 5 5 . 実験に対する考察

- 5 5 1 . 移動度

- 5 5 2 . しきい値

- 5-5-3. 基板バイアス効果

- 6.まとめ

- 7.謝辞

- 8.参考文献

## 1.目的

現在、社会に出回っているほとんどの電子機器には、MOS 集積回路が使われています。 その小型化、高集積化には目を見張るものがあります。

私は、その小型化する MOS トランジスタやそれを用いた電子回路の設計技術を習得する ために、MOS トランジスタの基礎理論や基本特性が基本知識として何よりも重要と考え、 それを中心とした調査をし、MOSトランジスタの基本特性に関する測定をしました。

#### 2. 方法

デジタル回路、アナログ回路などの回路に関する調査は、文献を通して行いました。MOSトランジスタの基本理論も文献を通して調査した後、MOSトランジスタの基本性能を測定しました。まず、カーブトレーサで大まかな特性の理解をした後、半導体パラメータアナライザにより MOSトランジスタのしきい値、移動度、基板バイアス効果などを測定し、MOSトランジスタの特性や回路設計に関する知識を深めました。

# 3.MOSトランジスタの基礎理論

## 3 - 1 . ドレイン電流特性

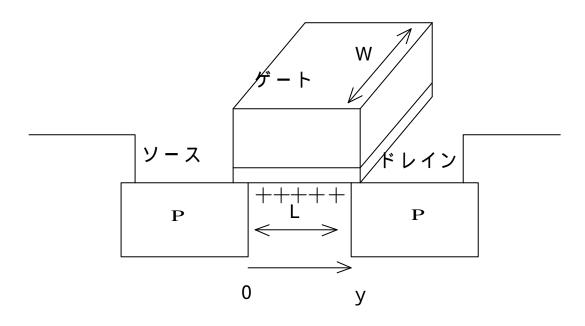

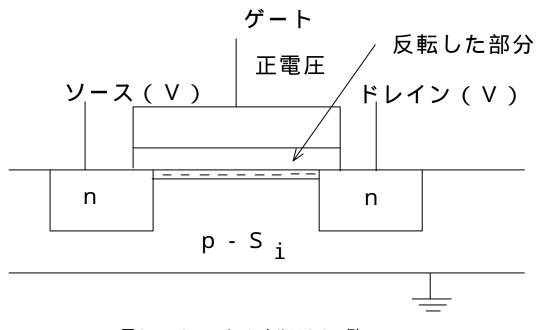

MOS トランジスタの電極は、キャリアの供給源であるソース、キャリアを取り出すドレイン、ソース・ドレイン間のチャネルのコンダクタンスを制御するゲート、そして半導体基板に電位を与える基板電極によって構成されている。

ゲート電圧が0でドレイン電流が流れないトランジスタを、エンハンスメント型トランジスタという。P チャンネルの場合、ある一定の正電圧をゲート電圧に印加することによりドレイン電流が0になる MOS トランジスタを、ディプリケーション型トランジスタという(ゲート電圧が0ではドレイン電流が流れる)。

# 3 1 1. 簡単なドレイン電流特性

図3.1 P チャンネルMOSトランジスタの概略図

ここでは、半導体表面での、エネルギーバンドの曲がりは、無視して、ソースからドレインまでの電位の変化だけを考慮する。チャネル内の任意の電位をV a とする。 ゲート電圧をV g として、q s c は単位面積あたりの半導体表面の電荷密度

$$q_{sc} = -(_{ox}/T_{ox})(V_g - V_a)$$

... (3 1)

であらわされる。

ゲート電圧を負にしていくと電子は半導体表面から内部の方に追い出され、表面にはドナーの正電荷が残る。さらにゲート電圧を負にすると、ゲート反転電圧(ゲートしきい値電圧ともいう)を境に半導体表面に正孔が誘起され始める。反転開始時における半導体表面の単位面積あたりのドナー密度を q i とすると(ドナーの電荷は、半導体表面から深さ方向に分布しているが、ここでは半導体表面に局在しているとして換算している。)

$$q_{i} = -(_{o_{x}}/T_{o_{x}}) V_{th}$$

... (3 - 2)

ここで、 $V_{th}$ は、ゲート反転電圧で、Va=0のところで定義する。

ゲート電圧をしきい値電圧 $V_{th}$  より負にした場合、半導体表面の正電荷の増加はすべて正孔が引き受けると仮定すると、半導体表面電荷密度 $q_{sc}$  はドナー電荷密度 $q_{ij}$  と反

転後に誘起される正孔電荷密度 q 。 の和になる。

$$q_{sc} = q_p + q_i \dots (3-3)$$

よって

$$q_p = -(_{ox}/T_{ox})(V_g - V_{th} - Va)$$

... (3 - 4)

この正孔がドレイン電圧  $V_D$  とソース電圧  $V_S$  の差によって発生する半導体表面に平行な電界 E(y) に加速されて走行する。正孔は電界方向に走行する。正孔電流を  $I_D(y)$  とすると

$$I_p(y) = \mu_{eff} \cdot W \cdot q_p \cdot E(y) \dots (3-5)$$

ただし、W: チャネル幅  $\mu_{eff}:$  正孔の実効的な移動度

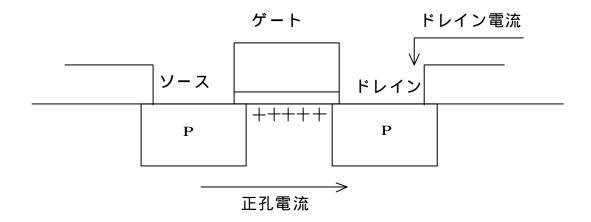

ソースから注入された正孔はすべてドレインに取り出されるために、正孔電流  $I_p(y)$  は場所 y によらず一定である。ここでドレイン電流  $I_D$  を図3.2に示すようにドレイン電極に入る電流とする。正孔電流  $I_D$  とドレイン電流  $I_D$  は方向が異なるため、- $I_D$  =  $I_D$  となり

$$I_{D} = - \mu_{eff} \cdot W \cdot q_{p} \cdot E(y)$$

... (3 - 6)

となる。

# 図3.2 MOSトランジスタの電流方向についての説明

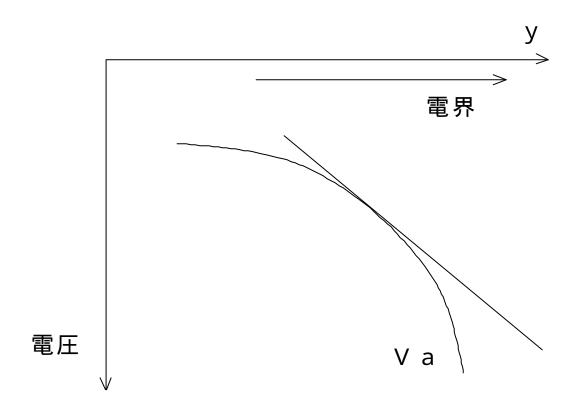

図3.3 方向について

電界は、上図に示すように正となる。

電界は半導体表面電位 Vaのyによる微係数で表されるので、

$$E(y) = -(dVa/dy) ...(3-7)$$

よって、(3-4)(3-6)(3-7)式より

$$I_D = \mu_{eff} \cdot W \cdot (\quad _{ox}/T_{ox})(V_g - V_{th} - Va)(dVa/dy) \quad ... (3 - 8)$$

上式をソースからドレインまで積分する。変数分離より

$$I_{D} \cdot dy = \mu_{eff} \cdot W \cdot (o_{x}/T_{ox})(V_{g} - V_{th} - Va) dVa$$

... (3 - 9)

左辺の y については 0 から L まで、右辺の V a については V s から V  $_{D}$  まで積分する。

$$I_{D}$$

·  $^{L}_{0}$  d y =  $\mu_{eff}$  · W · (  $_{ox}/T_{ox}$ ) ·  $^{V_{D}}_{Vs}$  (  $V_{g}$  -  $V_{th}$  -  $Va$  ) d  $Va$  ... ( 3 - 10)

$$I_D L = \mu_{eff} \cdot W \cdot (_{ox}/T_{ox}) [(V_g - V_{th}) Va - Va^2/2]^{V_D}_{Vs} \dots (3-11)$$

$$I_{D} = \mu_{eff} (W/L) ( _{ox}/T_{ox}) \{ (Vg - V_{th}) (V_{D} - Vs) - 1/2 (V_{D}^{2} - Vs^{2}) \}$$

... (3 - 12)

$$I_D = \mu_{eff} (W/L) (_{ox}/T_{ox}) (V_D - V_S) \{ (V_g - V_{th}) - (V_D + V_S)/2 \}$$

... (3 - 13)

というドレイン電流式を求めることができた。

- 3 2 . しきい値電圧

- 3 2 1 . フラットバンド電圧

以下は、Nチャンネルの例である。

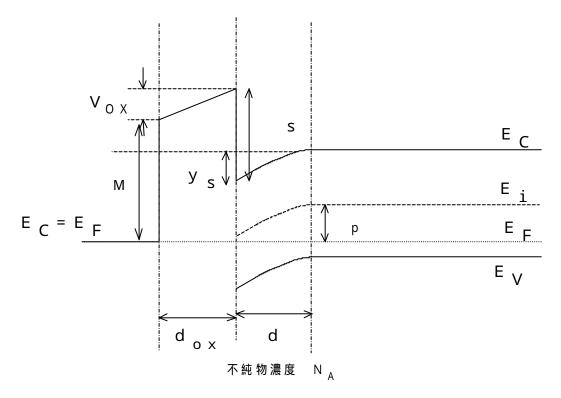

図3.4 ゲート電圧をかけない場合のエネルギーバンド構造の概略図

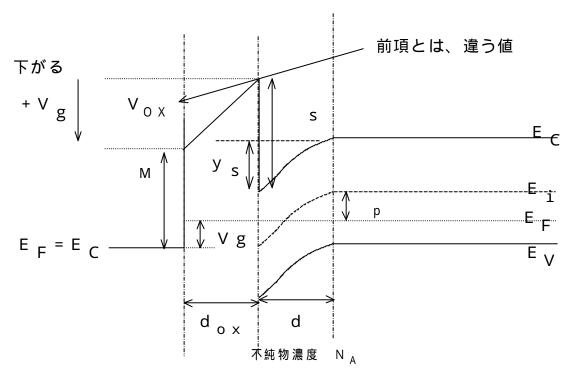

ここでは便宜上、真空の準位と酸化膜の伝導帯の底を同一準位として取り扱っている。 半導体表面に負電荷をもってアクセプタイオンの空乏層があらわれているとして、その空 乏層の深さを d 、表面ポテンシャル (表面におけるエネルギーバンドの曲がり)を y  $_{\rm S}$  とすると、ポワソン方程式を解くことにより、

$$y_S = \{qN_A/(2_S)\}d^2 = \{-Q/(2_S)\}d$$

... (3-14) ここでQは、半導体表面の電荷密度(単位面積あたり)である。 酸化膜にかかる電圧 $V_{OX}$  は、

$$V_{OX} = -Q/(_{OX}/d_{OX}) = (qN_Ad/_{OX})d_{OX}$$

...(3-15)

となる。

図3.5 ゲート電圧を加えたエネルギーバンド構造の概略図]

正のゲート電圧をかけた場合は上図のようになる。ただし、空乏層が延びたため、d の値は今までのものとは違い大きい値になっている。

半導体の仕事関数 Sェ は、

$$_{SI} = _{S} + (E_{g}/2) + _{p} ... (3 - 16)$$

ただし $_{\rm S}$ は、半導体の電子親和力である。 表面ポテンシャル $_{\rm S}$ は、前と同様に

$$y_S = \{ q N_A / (2_S) \} d^2 \dots (3-17)$$

上図で、ゲート金属のEFのレベルから半導体のEFレベルまでを見て

$$_{M} + V_{OX} - _{S} + y_{S} - (E_{g}/2) - _{p} = V_{g} \dots (3 - 18)$$

ここで  $_{M}$  は、ゲート金属の仕事関数である。 これから、 $V_{OX}+y_{S}$  を求めると

$$V_{OX} + y_{S} = V_{g} + S_{I} - M$$

... (3 - 19)

ここで  $V_{OX} + y_S = 0$  となるゲート電圧をフラットバンド電圧  $V_F$  と呼ぶと

$$V_F + S_I - M = 0$$

... (3 - 20)

したがって

$$V_F = {}_{M} - {}_{SI} \dots (3 - 21)$$

である。

# 3 - 2 - 2 . しきい値電圧

半導体表面で、 $E_i$ のレベルが $E_r$ より。pだけ下になり、基板内部の正孔濃度と半導体表面の電子濃度が同じになる状態を反転の開始と考える。すなわち、半導体表面のn化が、

半導体内部のp化と同じレベルと考える。 したがって

$$y_S = 2_p$$

... (3 - 22)

式(3-19)のV<sub>g</sub>にV<sub>F</sub>を代入し、(3-21)を用いて、

$$V_{OX} + 2_{p} = V_{th} - V_{F}$$

... (3 - 23)

また、式(3-14)(3-22)より

2

$$_{p} = (q N_{A}/2 _{S}) d^{2}$$

...  $(3 - 24)$

これから

$$d = \{(4_p s)/(qN_A)\}$$

...  $(3-25)$

ここから

式(3-14)(3-25)より

$$Q = -q N_A d = - (4_p \cdot s \cdot q \cdot N_A) \dots (3 - 26)$$

式(3-15)(3-26)より

$$V_{OX} = -Q/( O_{X}/d_{OX}) = (d_{OX}/S) (4_{p} \cdot S \cdot q \cdot N_{A})$$

... (3 - 27)

上式を、式(3-23)に代入して

$$(d_{OX}/_{S})(4_{p} \cdot _{S} \cdot q \cdot N_{A}) + 2_{p} = V_{th} - V_{F} ... (3 - 28)$$

V<sub>th</sub>を求めると

$$V_{th} = (d_{0X}/_{S})((4_{p}, S, q, N_{A})) + 2_{p} + V_{F}$$

...  $(3 - 29)$

式(3-16)(3-21)から

$$V_F = {}_{M} - {}_{SI} = {}_{M} - {}_{S} - (Eg/2) - {}_{p}$$

であるので

$$V_{th} = (d_{OX}/_{S})((4_{P} \cdot S \cdot q \cdot N_{A})) + M_{S} \cdot (Eg/2) + p$$

... (3 - 30)

となり、しきい値  $V_{th}$ を求めることができる。 ここで、

$$N_A = n_i \cdot e \times p \ (p/KT)$$

... (3 - 31)

であるので、一般的に、不純物  $N_A$  が増加すれば、しきい値は上昇する。 また、高温になればなるほど、  $_p$  が小さくなるため、しきい値  $V_{th}$  は低下する。

# 3-3.擬フェルミレベル

PN接合の熱平衡状態のエネルギーダイヤグラムは下のようになる。

# 図3.7 PN接合の熱平衡状態のエネルギーダイヤグラム

N型半導体とP型半導体を接合すると、N型領域から電子がP型領域に流れ込み、フェルミレベルE が一致して落ち着く。接合部のN型領域側では、ドナーイオンの正電荷、P型領域側では流れ込んできた電子が正孔と再結合してアクセプタイオンの負電荷が残る。すなわち接合部では、N型領域側ではドナーイオンの正電荷、P型領域側ではアクセプタイオンの負電荷からなる空乏層(電子も正孔も少ない領域)ができる。

N型領域中では、電子濃度nn、正孔濃度pnは、

$$N_D n_n = n_i e \times p (q_n/KT)$$

... (3 - 32)

$p_n = n_i e \times p (-q_n/KT)$  ... (3 - 33)

ただし、 $n_i$  =  $1.45 \times 10^{10}$  c m  $^{-3}$ 、室温では、KT/q = 2.6 m V

P型領域中では、正孔濃度po、電子濃度noは、

$$N_A$$

$p_p = n_i e \times p (q_p/KT)$  ... (3 - 34)

$n_p = n_i e \times p (-q_p/KT)$  ... (3 - 35)

接合部では、電位障壁として 「・・」ができる。

このPN接合に順方向の電圧を印加する。N型領域からP型領域に大量の電子が流れ込み、P型領域からはN型領域に大量の正孔が流れ込む。

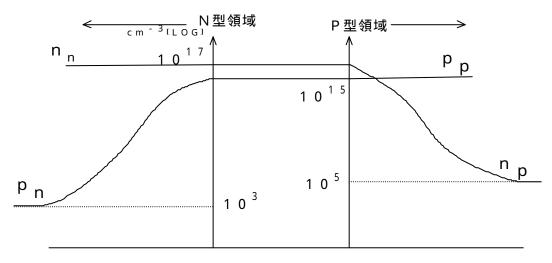

ここで、N型領域のドナー濃度 $N_D$ を $10^{17}$  c m  $^{-3}$ 、P型領域のアクセプタ濃度 $N_A$ を  $10^{15}$  c m  $^{-3}$  とする。N型領域、P型領域における電子、正孔の分布は、図3.8 のようになる。N型領域に入った電子は正孔と再結合して、P型領域の奥深くでは $n_p$  となる。

図3.8 電子・正孔の分布

このようにPN接合を順方向に印加した場合、接合部近辺では、P型領域にも多量の電子が存在し、また、N型領域にも多量の正孔が存在する。したがって、この部分では電子と正孔は熱平衡状態ではない。すなわち、電子と正孔に対するフェルミレベルは一致しない。電子と正孔に対しての別々のフェルミレベルを考え、それらを、擬(準)フェルミレベルという。

電子の擬フェルミレベルを $E_{Fn}$ 正孔の擬フェルミレベルを $E_{Fp}$ とすると、電子密度n、正孔密度pは、一般的に

$$n = n_i e \times p \{ q (E_{Fn} - E_i) / KT \} \dots (3 - 36)$$

$p = n_i e \times p \{ q (E_i - E_{Fp}) / KT \} \dots (3 - 37)$

とあらわすことができる。

電流は、電界によって流れるもの(ドリフト項)と、拡散によって流れるものがある。  $\times$ 方向への電子電流密度を  $\int_{\Gamma}$  とすると

$$J_n = q n \mu E + q D (d n/d x) ... (3 - 38)$$

ただしDは拡散係数、Eは電界、µは移動度である。

これから

$$J_{n} = q n_{i} \mu E \cdot e \times p \{ q (E_{Fn} - E_{i}) / K T \} + q D \cdot n_{i} e \times p \{ q (E_{Fn} - E_{i}) / K T \} \cdot q / K T \{ (dE_{Fn} / d \times) - (dE_{i} / d \times) \}$$

$$= q n_{i} \cdot e \times p \{ q (E_{Fn} - E_{i}) / K T \} [ \mu E + q D / K T \{ (dE_{Fn} / d \times) - (dE_{i} / d \times) \} ] \qquad ... (3 - 39)$$

ここで電界Eは、

$$E = - dV/dx = dE_{i}/dx$$

... (3 - 40)

であり、また、アインシュタインの関係式

$$\mu = q D/K T ... (3 - 41)$$

を用いると、式(3-39)は

$$J_n = q n_i \mu E \cdot e \times p \{ q (E_{Fn} - E_i) / K T \} \mu (d E_{Fn} / d \times)$$

... (3 - 42)

$J_n = q n \mu (d E_{Fn} / d \times)$  ... (3 - 43)

これは、非常に面白い結論で、ドリフト項と拡散項の合計の電流は、擬フェルミレベル の勾配だけを考えればよいことになる。

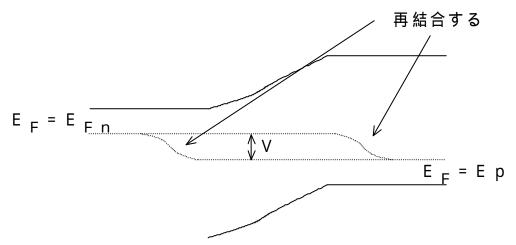

上式から、 $E_{Fn}$  の値は、電子濃度 n が大きい部分においては大きな変化はない。電子濃度 n が小さくなってくると  $E_{Fn}$  の値が急激に変化する。この様子を示すと図3.9 のようになる。接合部から離れた半導体の奥深くでは、 $E_{Fn}$ 、 $E_{Fp}$ は、 $E_{Fn}$ に一致する。

図3.9 フェルミレベルの分離したバンド構造の概略図

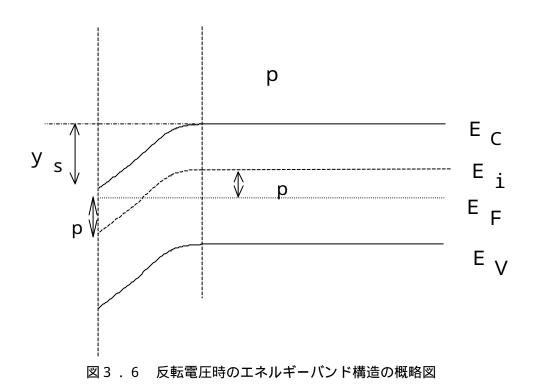

図3.9の場合は、PN接合の順方向電圧をかけた場合である。逆方向電圧をかけた場合は、接合部では $E_{Fn}$ が $E_{Fp}$ の上にくるようになる。

# 3 - 4 . 基板バイアス効果

図3.10 nチャンネルMOSの例

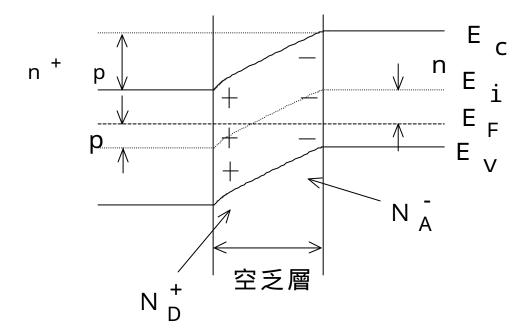

次にMOSトランジスタ構造を考える。図3.10 に示すように、P型シリコン基板を接地し、ソース、ドレインに正電圧Vを印加している。ゲートに強い正電圧を印加し、ソース・ドレイン間の半導体表面は反転(N型化)しているとする。そうすると、ソースとドレインと半導体表面のN型領域と基板のP型領域の間には、逆方向の電圧V が印加されていることになる。

したがって、N 型領域の擬フェルミレベル  $E_{Fn}$  は基板の正孔の基板の擬フェルミレベル  $E_{Fn}$  により V だけ下がる。

このような状態で半導体表面が、反転するには、エネルギーバンドの曲がりは 2 p + V にならなければならない。半導体表面の空乏層の深さを d として、ポワソン方程式を解くと、

$$y_S = 2_p + V$$

... (3 - 44)

$2_p + V = (q N_A/2_S) d^2$  ... (3 - 45)

$Q = -qN_AdJ$

$$2 p + V = (-Q/2 s) d ... (3-46)$$

N型化した部分と基板のP型の部分に逆方向バイアスがかかった場合は、空乏層の幅は延びるので、dおよびQの値は、バイアスがかかる前よりも大きくなる。

$$d = \{(2_{p} + V)/(qN_{A}/2_{S})\} \& \emptyset$$

$$Q = \{2_{S}(2_{p} + V) qN_{A}\} ...(3-47)$$

また、 $V_{OX}$  を酸化膜にかかる電圧とすると、 $CV_{OX} = -Q$ なので、

$$V_{OX} = q N_A d/(O_{OX}/d_{OX})$$

=  $d_{OX}/O_{OX} \{2_S(2_P+V) q N_A\} \dots (3-48)$

よって、上式より、N型領域にかかる電圧 V が上昇すれば、酸化膜にかかる電圧も上昇することが理解できる。

また、しきい値電圧 (ソースの電位を基準にして)は、

$$V_{th} = V_{OX} + 2_{p} + V_{F}$$

... (3 - 49)

で、Vょは、フラットバンド電圧であるから、

$$V_{th} = d_{OX}/_{OX} \{2_{S}(2_{p}+V) q N_{A}\} + 2_{p}+V_{F}$$

... (3-50)

よって、逆方向電圧V が大きいほどしきい値電圧が上昇する。順方向電圧(負の電圧)は、かけるとしきい値電圧は下降する。

このように、しきい値電圧が変化する現象を、基板バイアス効果という。

## 4.移動度

# 4-1.移動度とは

電子や正孔は半導体中の電界により加速されエネルギーを得るが、一方熱振動する格子原子やイオン化した不純物原子にぶつかることによりエネルギーを失う。よって、電子や正孔は電界によって無限に加速されることはなく、電界に比例した一定の速度を得ることになる。その速度をドリフト速度という。その方向は、電子の場合は電界の方向とは逆向きで、正孔の場合は電界の方向と同じである。

$$v = \mu E$$

... (4 - 1)

ここで、 ν はドリフト速度〔m/s 〕 μ は移動度〔m²/V・s 〕 E は電界〔V/m〕

移動度は、前述するように、熱振動する格子原子やイオン化した不純物原子によって決まる。半導体中の不純物濃度が高ければ移動度が低下する。熱振動する格子原子の影響は温度が上がれば強くなる。

電流密度 J は電界 E に比例している。

$$J = E/ = E \dots (4 - 2)$$

は抵抗率、は導電率で、導電率は抵抗率の逆数。

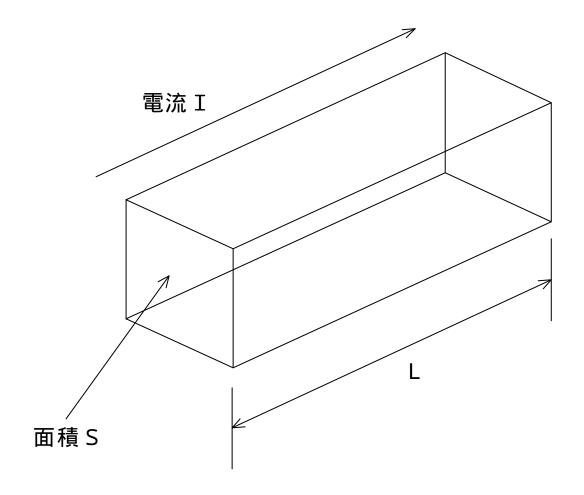

図4.1 導体の誘電率の測定

電流 I が一定面積 S、長さ L の半導体を通過しているとして、その両端の電位を V 1、 V 2 とすると、電界 E は ( V 1 - V 2 ) / L となる。 よって、

$$J = I/S = (V1 - V2)/L ...(4 - 3)$$

一方、オームの法則より

これからRを求めると

$$R = (V1 - V2)/I = (V1 - V2)/(SJ) ...(4 - 5)$$

式(4-3)より

$$R = (V1 - V2)/{S (V1 - V2)/L}$$

$$= (L/S)(1/)$$

$$= (L/S) ... (4 - 6)$$

また、導電率は抵抗率の逆数である。

一方、電流密度」は、半導体の電子または正孔のキャリア密度をnとすると

$$J = n e v ... (4 - 7)$$

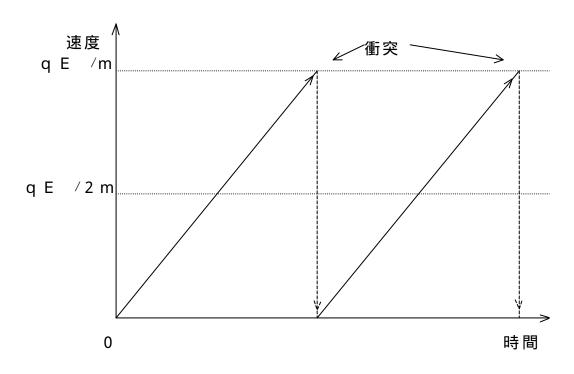

ここで、電子の場合について考える。電界 E を電子に加えると e E の力が働くので加速度 a は、電子の質量mとすると

$$a = e E/m$$

... (4 - 8)

図4.2 衝突の平均時間

また、速度が衝突により最高値から零に戻るものと考える。衝突の間の時間を とすると平均速度 v は、

$$v = (1/2) a = (1/2) e E /m ... (4-9)$$

式(4-7)に代入して

$$J = (1/2) n e^{2} E /m ... (4 - 10)$$

よって

$$= (1/2) n e^{2} /m ... (4 - 11)$$

導電率は自由電子の密度に比例する。

$$\mu = (1/2) e /m ... (4 - 12)$$

$e = 2 m \mu ... (4 - 13)$

これを式(4-11)に代入すると

電子と正孔が電流を運ぶ半導体の場合は、

$$= n e \mu_n + p e \mu_p$$

... (4 - 15)

nは電子の密度、pは正孔の密度

と表すことができる。

# 4 - 2 . MOSトランジスタの移動度について

MOSトランジスタの移動度については、電界効果移動度と実効移動度が用いられている。これらの移動度は、トランジスタの非飽和領域において以下のように定義されている。 微小ドレイン電圧領域における相互コンダクタンスは、

gm I

$$_{D}/$$

V  $_{g}$  ... ( 4 - 1 6 )

ここで、ドレインの電流特性を簡単な式で表現してみる。

$$I_D = \mu \cdot (W/L) \cdot (O \times /T O \times) \cdot (V_D) \{V_g - V_{th} - V_D / 2\}$$

... (4 - 17)

移動度  $\mu$  のゲート電圧依存度を無視して、上式を  $V_g$  で微分して g mを求める。

$$gm = \mu (W/L)(ox/Tox)V_D ...(4-18)$$

式(4 - 18)のg mを測定して求められる移動度が、電界効果移動度  $\mu_{FE}$ である。よって、

$$\mu_{FE} = gm(L/W)(Tox/ox)1/V_D ...(4-19)$$

一方、実効移動度は、非飽和領域におけるドレイン特性

$$I_D = \mu (W/L)(_{OX}/T_{OX})(V_g - V_{th}) V d$$

... (4 - 20)

より、求める移動度で

$$\mu_{eff} = I_D/(V_{OX} - V_{th})(L/W)(T_{OX}/_{OX})(1/V_D) \dots (4 - 21)$$

と定義されている。

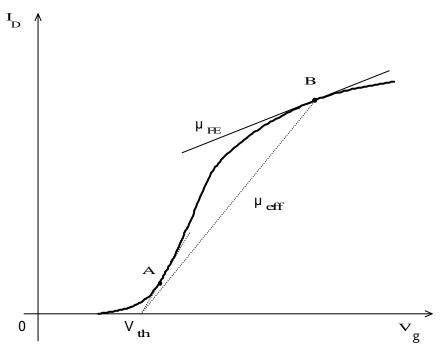

μ<sub>FE</sub>、μ<sub>eff</sub>の関係を図示すると、

図 4 . 3 MOSトランジスタの I  $_{\text{D}}$  - V  $_{\text{g}}$ 特性

勾配の最大点 A の接線と、  $V_g$ 軸の交点が、 しきい値電圧  $V_{th}$ である。 測定点 B と  $V_{th}$ と の線の傾きから求められる移動度が  $\mu_{eff}$ であり、 B 点の接線の傾きが  $\mu_{EF}$ である。

## 5.MOSトランジスタの測定

#### 5 - 1 . 実験器具

カーブトレーサについて

半導体素子の特性を測定するための機器です。

コレクタ電流の感度が、 $2 n A/d i v \sim 2 A/d i v$ 。確度  $\pm 3 \%$ 、 $\pm 1 n A$ 。コレクタ電圧の感度が、 $5 0 m A/d i v \sim 2 0 0 V/d i v$ 。感度  $\pm 3 \%$ 。ベース電圧  $5 0 m A/d i v \sim 2 V/d i v$ 。確度  $\pm 3 \%$ のもので測定。

例えば、バイポーラトランジスタの、コレクタ電流の特性を測定する際は、横軸にコレクタ電圧(エミッタ - コレクタ)、縦軸にコレクタ電流、そして、ステップ状にベース電流を印加する。

また、MOSトランジスタのドレイン電流測定を行う際には、横軸にドレイン電圧を、 縦軸にドレイン電流を、ゲートに電圧をステップ状にかけます。

#### 半導体パラメータアナライザについて

簡単にいうと、解析機能やデータ処理機能を持ち多機能で、高精度の測定器である。測定のユニットは、グランドユニット(GNDU)、ソースモニタユニット(SMU)、電圧ソースユニット(VSU)、電圧モニタユニット(VMU)、パルスジェネレータユニット(PGU)によって成り立っている。以下の測定では、このユニット部分として、グランドユニット、ソースモニタユニット、を使用して測定しました。また、SMUには、測定の値の関係上最も適切だと思われる±100Vまたは、±100mAまで、最大出力電力2Wの、ミディアムパワーSMUを使用した。この他には、±200Vまたは、±1A、最大出力電圧20WのハイパワーSMUなどある。

#### 半導体パラメータアナライザの使用方法

#### その1

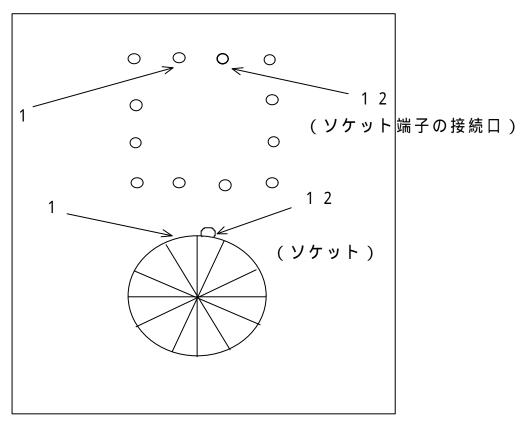

まず、半導体パラメータアナライザに接続されたテストフィクスチャのソケットに、素子を挿入する。そして、ソケット端子とテストフィクスチャの端子をつなぎます。ちなみに、ソケットとソケット端子の関係は、以下のようになっています(TOパッケージの場合)。

図5.1 ソケットとソケット端子への接続口の概略図

# その2

その後、テストフィクスチャにおさめた素子の端子に対して、半導体パラメータアナライザ上で電圧電流印加や測定の条件付けしていきます。まず、モードをどうするか。モードには、VモードとIモードがある。Vモードは、電流をかけて電圧を測定する。Iモードは、その逆で、電圧をかけて、電流を測定する。

そして、掃引測定をする場合は、VAR1、VAR2などを使用し階段状電圧の印加方法を決める。掃引のタイプは、片道掃引と、往復掃引があります。

# その3

掃引のタイプを決定した後、詳しい電圧値、電流値の印加の仕方を決定します。まず、 どの値からスタートするか、どの値でストップするか、横軸、縦軸の値は何にするか、測 定項目を何点にするか、グラフの寸法はどの値にするか、もし関数を組み込んだ値を出し たいのであれば、どのような関数を、どの値に組み込むのかなどである。

#### その4

以上の、設定を経て測定した後、その値を解析する。測定値の出力方法は、グラフ表示とリスト表示がある。このリスト表示も、何を表示するかあらかじめ設定のところで登録しておく。その出力された値に対し、微分、積分、最大値、最小値、四則演算などの数値計算を、半導体パラメータアナライザで行うことができる。以下の実験も、この機能を用いて測定、解析等を行っている。また、測定値を外部の機器に出力したい場合は、テキスト形式で出力することが可能である。

## 5 - 2 . 測定した MOS トランジスタ

以下の測定では、

- (1) P チャンネルMOSトランジスタ(M33)、基板の抵抗率 8.45 cm 、酸 化膜層2080 のもの。チャネル長200μm 、幅600μm 、シリコン結 晶面は(322)面のものと、

- (2) PチャンネルMOSトランジスタ(M35) 基板の抵抗率 8.3 cm 、酸化 膜層 2080 のもの。チャネル長 200 $\mu$ m 、幅 600 $\mu$ m 、シリコン結晶 面は (111)面のものを使用している。

- (3) P チャンネルMOSトランジスタ(M37)、基板の抵抗率 8.0 cm 、酸化 膜層2080 のもの。チャネル長200μm 、幅600μm 、シリコン結晶 面は (411)面のものと、

これらのサンプルは、移動度測定用に製作されたものであり、チャネル長、チャネル幅が大きく作られている。

#### 5 - 3 . 実験方法

上記の試料を用いてドレインに - 50 m V の負の電圧を、ゲートに負の電圧を0~15 V の間で変化させて加え、 $I_D$  -  $V_g$ 特性をとり、その測定データからしきい値電圧、移動度を求める。

また、同条件で基板に正電圧を0~5 Vまで印加し、それによるしきい値電圧、移動度

の変化を測定し基板バイアス効果を調べる。また、使用する機器は上記で説明した、半導体パラメータアナライザにより測定する。

## 5 - 4 . 実験結果

以下の実験データは、半導体パラメータアナライザにより測定したデータを、エクセル により、グラフに表示したものです。

## 5 - 4 - 1 . ドレイン電流特性

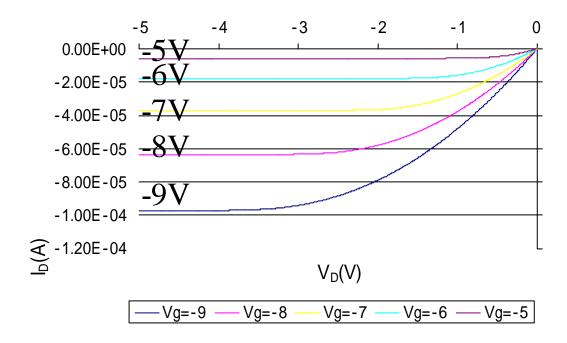

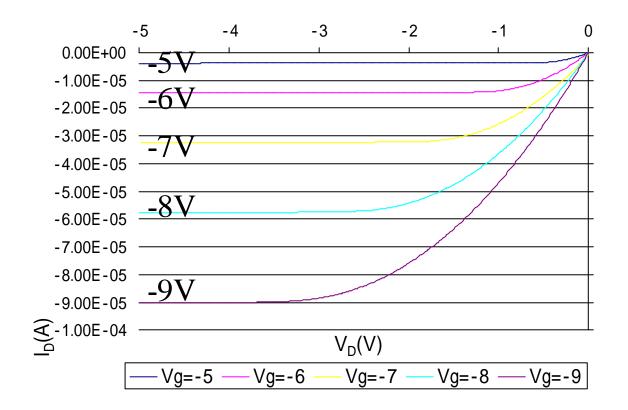

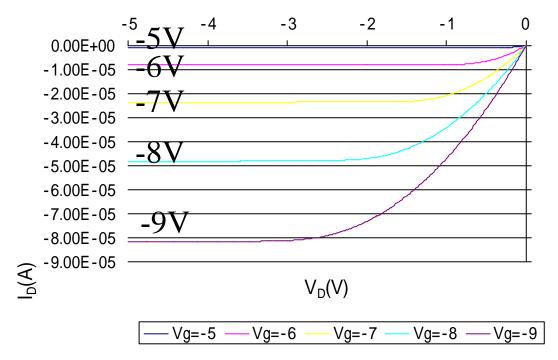

試料の特性を全体的に把握するため、まずドレイン電流特性を測定し、その結果を図5.2~図5.4に示す。

図5.2 (M33)のI<sub>D</sub>-V<sub>D</sub>特性

横軸が、ドレイン電圧  $V_D$ (0~-5 V)、横軸がドレイン電流  $I_D$ (0~-12 mA)である。ゲート電圧  $V_g$ を、-5~-9 Vの間を 1 V ステップに変化させている。

図5.3 (M35)のI<sub>D</sub>-V<sub>D</sub>特性

横軸が、ドレイン電圧  $V_D$ (0~-5 V)、横軸がドレイン電流  $I_D$ (0~-10 mA)である。ゲート電圧  $V_g$ を、-5~-9 Vの間を 1 V ステップに変化させている。

図5.4 (M37)のI<sub>D</sub>-V<sub>D</sub>特性

横軸が、ドレイン電圧  $V_D(0\sim -5\ V)$ 、横軸がドレイン電流  $I_D(0\sim -9\ mA)$  である。 ゲート電圧  $V_g$ を、 - 5  $\sim$  -9 Vの間を 1 V ステップに変化させている。

図 5 . 2、図 5 . 3、図 5 . 4の測定により、試料の P チャネル MOS トランジスタ M 3 3、M 3 5、M 3 7 は正常に動作していることがわかる。

# 5 - 4 - 2 . 移動度

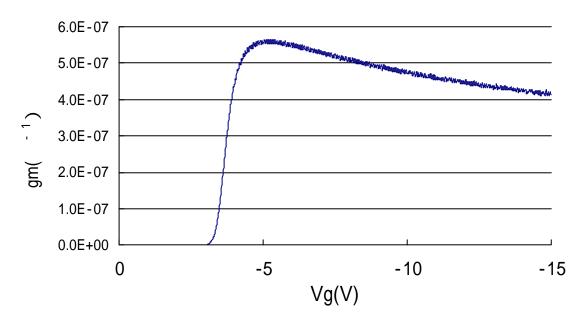

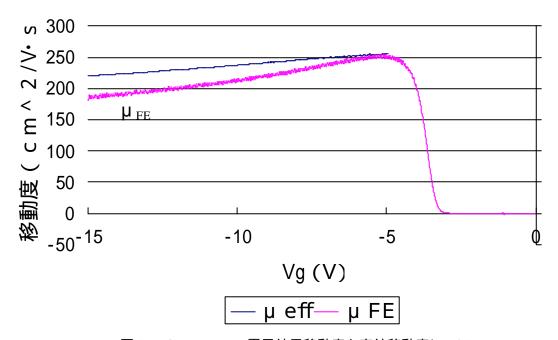

M33、M35、M37 を用いて、まず相互コンダクタンスを測定し、その値を用いて実効移動、電界効果移動度を求めた。

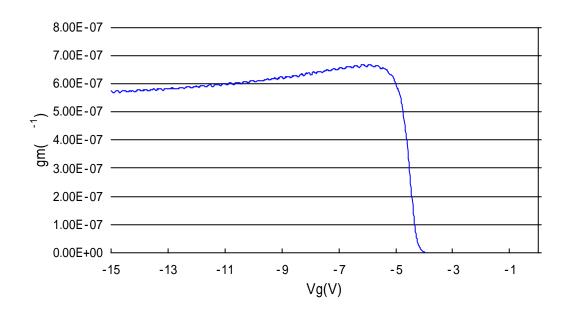

図 5 . 5 (M33)の相互コンダクタンスのゲート電圧による変化 横軸にゲート電圧  $V_g$  (0 ~ - 15V) 縦軸に相互コンダクタンス g m ( $^{-1}$ )である。 ドレイン電圧  $V_D$  - 50 mV、を印加してゲート電圧とドレイン電圧を測定しドレイン電流をゲート電圧で微分して求めた。

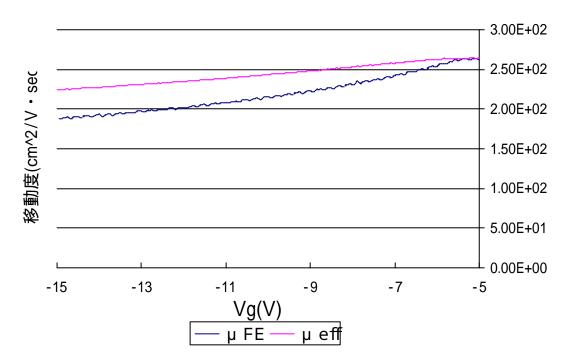

図 5 . 6 (M33)電界効果移動度と実効移動度について 図 5 . 5 の結果から、電界効果移動度と実効移動度を求めてあらわしたものである。 下の曲線が電界効果移動度  $\mu_{\rm FE}$  、上の曲線は実効移動度  $\mu_{\rm eff}$ である。

図5.7 (M35)の相互コンダクタンスのゲート電圧による変化

横軸にゲート電圧  $V_g$  (0 ~ - 15 V ) 縦軸に相互コンダクタンス g m (  $^{-1}$  ) である。 ドレイン電圧  $V_D$  - 50 m V を印加してゲート電圧とドレイン電圧を測定しドレイン電流をゲート電圧で微分して求めた。

図5.8 (M35)電界効果移動度と実効移動度について

図 5 . 7 の結果から、電界効果移動度と実効移動度を求めてあらわしたものである。 下の曲線が電界効果移動度  $\mu_{FE}$  上の曲線は実効移動度  $\mu_{eff}$ である。

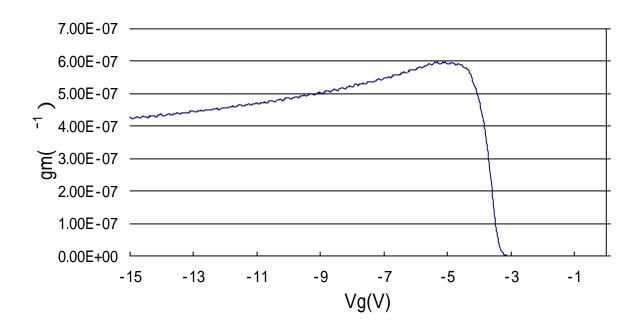

図5.9 (M37)の相互コンダクタンスのゲート電圧による変化

横軸にゲート電圧  $V_g$  (0 ~ - 15 V) 縦軸に相互コンダクタンス g m (  $^{-1}$ ) である。 ドレイン電圧  $V_D$  - 50 m V、を印加してゲート電圧とドレイン電圧を測定しドレイン電流をゲート電圧で微分して求めた。

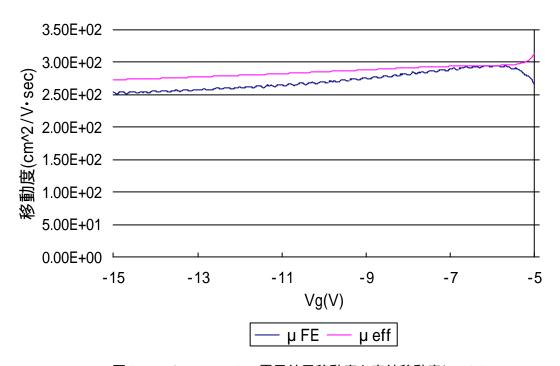

図5.10 (M37)電界効果移動度と実効移動度について

図 5 . 9 の結果から、電界効果移動度と実効移動度を求めてあらわしたものである。 下の曲線が電界効果移動度  $\mu_{FE}$  上の曲線は実効移動度  $\mu_{eff}$ である。

# 5 - 4 - 3 . 基板バイアス効果

# (1) 基板バイアスにおけるしきい値の変化

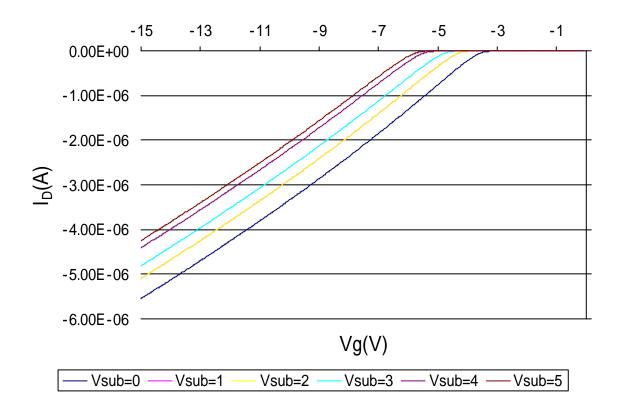

以下の図は、基板に0~5Vまで電圧を変化させて印加したものである。

図 5 . 1 1 M 3 3 の基板バイアス効果によるしきい値の変化の実測データ 横軸にゲート電圧  $V_g$  (0 ~ 15 V) 縦軸にドレイン電流  $I_D$  を示した。また基板に正電圧を (0 ~ 5 V) 変化させて印加した時のしきい値の変化を示したものである。 右から、基板電圧が、0、1、2、3、4、5 V である。

図5.11から、しきい値を求めた結果を表5.1に示す。

表5.1 基板バイアス効果によるしきい値の変化

| 基板電圧(V) | しきい値電圧(V)       |

|---------|-----------------|

| 0       | - 3 . 6 8 1 3 6 |

| 1       | - 4 . 3 8 1 5 7 |

| 2       | - 4 . 8 6 0 2 5 |

| 3       | - 5 . 2 4 6 2 7 |

| 4       | - 5 . 5 7 4 9 3 |

| 5       | - 5 . 8 7 8 7 2 |

# (2)基板バイアス効果による移動度の変化

基板バイアスを変化させて電界移動度を測定し、その結果を図5.12、図5.13、図5.14に示した。

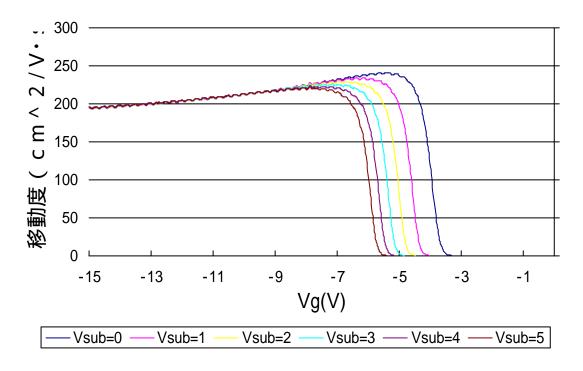

図5.12 M33の基板バイアス効果による電界効果移動度の変化

横軸にゲート電圧  $V_g$  (0 ~ - 15) 縦軸に移動度  $\mu$  (c  $m^2/V \cdot sec$ ) を示した。ドレイン電流  $I_D$  - 50 mV を印加して基板に 0 ~ 5 V の正電荷を印加した時における移動度の変化を示したものである。

右から、基板電圧が、0、1、2、3、4、5 V である。

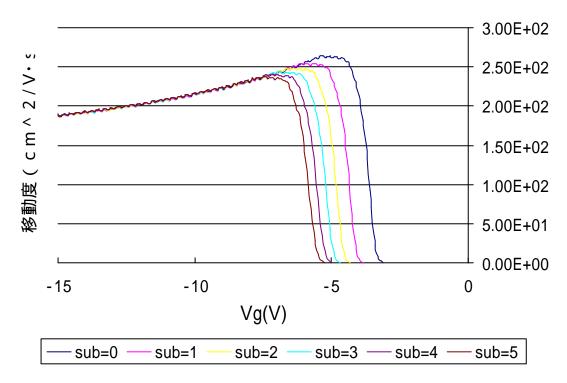

図5.13 M35の基板バイアス効果による電界効果移動度の例

横軸にゲート電圧  $V_g$  (0 ~ - 15) 縦軸に移動度  $\mu$  (c  $m^2/V \cdot sec$ ) を示した。ドレイン電流  $I_D$  - 50 mV を印加して基板に 0 ~ 5 V の正電荷を印加した時における移動度の変化を示したものである。

右から、基板電圧が、0、1、2、3、4、5Vである。

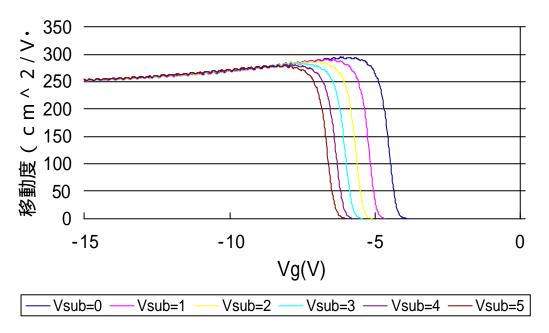

図5.14 M37の基板バイアス効果による電界効果移動度の例

横軸にゲート電圧  $V_g$  (0 ~ - 15)、縦軸に移動度  $\mu$  (c  $m^2/V$ ・sec)を示した。ドレイン電流  $I_D$  - 50 mV を印加して、基板に 0 ~ 5 V の正電荷を印加した時における移動度の変化を示したものである。

右から、基板電圧が、0、1、2、3、4、5 V である。

## 5 - 5 . 実験の考察

## 5-5-1.移動度

電界効果移動度と実効移動度は、図4.3において定義したように最大勾配点 A では同じ値になるはずである。図5.6、図5.8、図5.10の測定結果でも $V_g = V_{th}$ の近傍で $\mu_{eff}$ 、 $\mu_{FE}$ が最大となる点で $\mu_{eff}$ 、 $\mu_{FE}$ が一致していることが分かる。

また、両移動度は、図5.6、図5.8、図5.10の実測データからも明らかに、ゲート電圧の上昇により減少する。ゲート電圧依存性は実効移動度に比べ電界効果移動度の方が大きく、一般的に $\mu_{eff}>\mu_{FE}$ が成立している。移動度が、ゲート電圧によって減少するのは、ゲート電圧の上昇によってキャリア(この場合は正孔)が、半導体表面の狭いところに閉じ込められ、表面で散乱を激しく受けるためと考えられる。このようなゲート電圧による移動度の低下により、図4.3の曲線は勾配が減少する曲線となり、定義により $\mu_{eff}>\mu_{FE}$ となり、その結果が測定されている。

## 5-5-2.しきい値

Pチャネルトランジスタにおいて基板に正電圧を加えればしきい値が上昇する。このことにより、ゲート、ソース間により小さな実効的な電圧がかかった状態になり、半導体表面にたまる正孔は少なくなり移動度は小さな値から始まる。

また、3つのPチャネルMOSトランジスタを比べてみると、幾分かの違いが見えるが、これは主に結晶面による違いと思われる。

図5.6より MOS トランジスタの移動度は、ゲート電圧 - 5 V の場合と - 15 V の場合を比較すると、20%ほど減少している。図5.13においても基板バイアスの状態において、移動度がかなりの大きさで変化している。このことにより、MOS トランジスタの移動度を一様と考えて回路設計を進めることはできないことがわかる。

#### 5-5 3. 基板バイアス効果

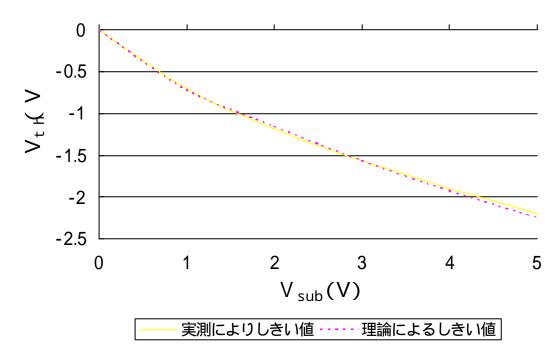

基板バイアス効果を測定したサンプルの基板の抵抗率は  $8.45~\mathrm{cm}$  である。基板の不純物濃度は、基板の抵抗率と不純物濃度との関係を実測した値から決定した(  $1.70\times10^{15}\mathrm{cm}^{-3}$  )。 ゲート酸化膜厚は 2080 ( ) である。

。は、式(3-31)より求めることができる。

ただし、真性フェルミレベル下でのキャリア数は、 $n_i = 1.45 \times 10^{10} (cm^{-3}) KT/q = 2.6 (mV)$ を用いた。

またしきい値は、式(3-50)より

$V_{th} = {}_{OX}/d_{OX} \{ 2 {}_{S} ( 2 {}_{P} + V ) q N_{A} \} + 2 {}_{P} + V_{F}$

で計算できる。

上記の式は、酸化膜中のイオンの量を考慮してないため、絶対値はあわない。そこで、 基板電圧によるしきい値電圧の変化分を評価した。

実測値と計算値を図5.15に示す。両者の値は非常によく一致した。

図5.15 しきい値の比較 M33のしきい値について、実測値と計算値との比較

# 6.まとめ

MOS トランジスタに関してドレイン電流特性、フラットバンド電圧、しきい値電圧、擬フェルミレベル、移動度など調査し、MOSトランジスタの動作を詳しく知ることができた。移動度としきい値電圧については、基板バイアス効果も含めて半導体パラメータアナライザを用いて測定し、理論と実験の一致も見ることができ、回路設計のための基礎知識を充分に得ることができた。

# 7.謝辞

この卒業研究を製作するのにあたり、高知工科大学、電子・光システム工学科、原央教授には甚大なる協力をいただきました。先生なしでは、この卒業研究は完成しませんでした。深く感謝いたします。

輪講でお世話になった、矢野政顕教授、河津哲教授、橘昌良助教授ありがとうございま

した。

また同じ研究室の岡田吉央氏、木村知史氏、小松勇貴氏、白木正章氏、新妻研作氏、河津研究室、矢野研究室、橘研究室の皆さん楽しい研究室作りありがとうございました。基礎知識を教えていただいた先生方ありがとうございました。

皆さんの、健康とご多幸をお祈りして終わらせていただきます。

# 9.参考文献

[1]原央 他 著: "MOS トランジスタの動作理論"近代科学社 P169 (1980)

[2]清水潤治 著:"半導体工学の基礎"P256 コロナ社(1986)

[3]原央 著: "MOS 集積回路の基礎"P259 近代科学社(1992)

[4] S.M.SZE 著: "半導体デバイス" P557 産業図書 (1987)

[5] Andorew S.Grove 著:"半導体デバイスの基礎"P411 オーム社(1995)