# ウェハボンディングによる Ge/Si ヘテロ接合フォトダイオードの作製

Fabrication of Ge/Si Heterojunction Photodiodes by Wafer Bonding

指導教員

神戸 宏

1055079

大西 健一

平成 15 年 1 月 27 日

高知工科大学 電子・光システム工学コ - ス

# ウェハボンディングによる Ge/Si ヘテロ接合フォトダイオードの作製

平成 14 年度 高知工科大学大学院工学研究科 基盤工学専攻 電子・光システムコース 大西 健一

大量の情報のやりとりが可能な光ファイバ通信システムは、幹線系のみならず加入者系にも導入されつつある。光ファイバが最低損失となる 1.55 µm 帯の受光素子がより高性能で安価になれば、光ファイバ通信のより一層の拡大が可能となる。

本研究は、現在広〈用いられている InGaAs/InP-APD(アバランシフォトダイオード) に替わり、 光ファイバ通信用高性能受光素子として、新たに Ge/Si-APD を提案し、その実現を目的とし 進めたものである。すなわち、光吸収層を InGaAs から Ge に、なだれ増倍層を InP から Si に替 えた構造を提案する。これにより、1.55 µ m 帯の光に対して十分に応答し、かつなだれ増倍 層で発生する過剰雑音を低減した APD が実現できる。

本研究では、光通信用の受光素子として、理論検討から pn-Si/p-Ge-APD の有効性を明らかにした。また、p-Si 層に必要な不純物濃度と厚みの関係を求め、それに基づいて設計を行った。

次に素子実現を目指し、ウェハボンディングを用いて Si/Ge ヘテロ接合形成を試みた。その結果、p-Ge/p-Ge、p-Ge/n-Si、p-Ge/p-Si の各々の組み合わせでボンディング条件を明らかにし、目的とする pn-Si/p-Ge のボンディング成功に至った。

ウェハボンディング成功率あるいは接着力向上のため、工程の詳細を検討した結果、pn-Si/p-Ge において、90%程度の歩留りで、接合形成に成功した。

目指す APD としての動作のため必要なメサ型構造作製の工程を行い、工程毎に素子の I-V 特性の変化を調べた。

Au をマスクに用いて、メサ構造作製に必要な Si の深いエッチングを成功し、最終目標であるメサ型構造の作製に成功した。

フォトダイオード、あるいは APD としての動作確認、つまり 1.55 µmの光に対しての明確な応答はまだ確認できていないが、暗電流(特に漏れ電流)の低減、接合からの空乏層の拡大などにより可能になると考えられ、今後検討する

# <u>目次</u>

# 第1章 緒言

| 1.2 本研究の意義               | 0    |

|--------------------------|------|

|                          | Z    |

|                          |      |

| 2章 フォトダイオードおよ            | びAPD |

|                          |      |

| 2.1 はじめに                 | 4    |

| 2.2 光の吸収                 |      |

| 2.3 太陽電池                 |      |

| 2.4 フォトダイオード             |      |

| 2.4.1 応答速度               |      |

| 2.4.2 暗電流                |      |

| 2.5 アバランシフォトダイオード (APD)  |      |

| 2.5.1 過剰雑音               |      |

| 2.6 本章のまとめ               |      |

| 2.6 本草のまとめ               | 14   |

|                          |      |

| 第3章 Ge/Si-APD の基本構       | 造と設計 |

|                          |      |

| 3.1 Ge/Si-APD <b>の構造</b> | 15   |

| 3.2 吸収係数                 | 15   |

| 3.3 基板材料                 |      |

| 3.4 アパランシブレークダウン電圧       |      |

| 3.5 空乏層幅                 |      |

| 3.5.1 拡散電圧 VD            |      |

| 3.5.2 空乏層幅               |      |

|                          |      |

| 3.7 ヘテロ接合                | 22   |

# 第4章 ウェハボンディング

| 4.1 | ワェハボンティング         | 25 |

|-----|-------------------|----|

| 4.2 | ボンディングプロセスと成功率の改善 | 25 |

| 4.3 | 前処理による特性の改善       | 28 |

| 4.4 | ボンディング結果          | 29 |

| 4.5 | ホットプレート (HP)      | 29 |

| 4.6 | アニール              | 30 |

| 4.7 | 本章のまとめ            | 30 |

|     | 第5章 素子製作          |    |

| 5.1 | ウェハボンディング         | 31 |

| 5.2 | 研磨                | 32 |

| 5.3 | エッチング             | 34 |

| 5.4 | 電極付け              | 35 |

| 5.5 | メサ型エッチング          | 35 |

| 5.6 | 本章のまとめ            | 36 |

|     | <u>第6章 特性の改善</u>  |    |

| 6.1 | メサ型エッチング          | 37 |

| 6.2 | 処理工程の提案           | 39 |

| 6.3 | 光起電力の測定           | 40 |

| 6.4 | 本章のまとめ            | 41 |

|     | <u>第7章 結言</u>     |    |

| 謝辞  | ¥                 | 43 |

| 参考  | <b>≶文献</b>        | 44 |

## 第1章 緒言

高度情報化社会と言われ、大量の情報の伝送処理技術が要求されている。特に情報通信においては各家庭まで光ファイバが敷設されるようになり、それを束ねた幹線系ではTb/sからPb/sの光ファイバ通信システムの構築がなされつつある。

本研究は光ファイバ通信用受光素子に関し、新たな半導体材料を組み合わせたフォトダイオード構造を提案し、より高性能な受光素子の実現を目指したものである。

以下本章では本研究の目的と意義を明らかにする。

### 1.1 受光素子の役割と本研究の目的

光ファイバ通信システムの基本構成は、情報源からの電気信号を発光素子により光信号に変換し(E/O変換) 光ファイバを通して伝送した後、受光素子に入力され電気信号に戻す(O/E変換) というものである。このような光ファイバ通信システムにおいて、システムの性能を決めるのは発光素子や光ファイバの特性だけではなく受光素子の特性にも大きく依存する。

受光素子に要求される条件として

必要とされる波長に対して量子効率が良いこと

周波数応答特性が良いこと

付加雑音が小さいこと

温度・湿度などの外部条件に対して、特性が変化しないこと

低起電力で動作が可能なこと

などが挙げられる[1]。これらの条件を満たす受光素子としては、半導体素子であるフォトダイオード (Photodiode; PD) やアバランシフォトダイオード (Avalanche Photodiode; APD) がある。現在の光ファイバ通信では InGaAs PIN-PD や、InGaAs/InP-APD などが用いられている。

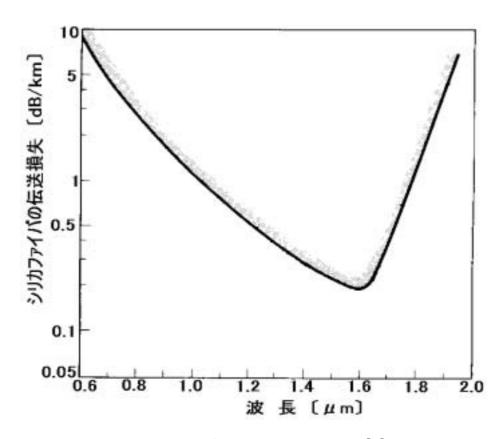

図 1 光ファイバ (シリカ)の伝送損失 [1]

InGaAs/InP を用いた PD、APD が使われるのは、光ファイバ伝送損失の波長依存性に依っている。図 1 は波長に対する光ファイバ伝送損失の波長依存性を示した図である。図 1 に示すように波長 1.55 μm 帯で最小の損失となる。現在光ファイバの損失はほぼ理論限界まできているとされ、その伝送損失は 0.154 d B / k mである[1]。このため受光素子は 1.55 μm 帯の光に応答するバンドギャップ 0.8eV 以下の半導体材料が必要であり、実際に InP に格子整合した InGaAs が用いられている。

本研究では、長波長(1.55 µm)帯に応答する受光素子材料として、InGaAs/InPに替わる新しい素材を提案する。これにより、より高性能でしかも安価な PD または APD を実現することができていると考えられる。

## 1.2 本研究の意義

現在光ファイバ通信で広く用いられている受光素子は上述したようにInGaAs-PD および InGaAs/InP APD である。InGaAs/InP-APD では、InGaAs

しかし、Si では 1.55 μm の光に応答しない。このため InP の場合と同様に別の半導体材料を用いて光吸収層となる領域を設ける必要がある。

ごく最近 Si をなだれ増倍層とし、光吸収層を InGaAs とする APD を実現したという報告がある[9,10]。本研究ではこれに対し光吸収層として InGaAs よりも安価に入手できる Ge を用いることを提案する。

本研究では、まずGe/Siへテロ接合を用いたフォトダイオードの実現を目指し不純物濃度などの設計を行った。次に、Si上に格子定数の大きな差のあるGeをエピタキシャル成長させるのは難しいとされているので、本研究ではGe/Siへテロ接合の作製のために、ウェハボンディングという手法を用いた。

Ge と Si のウェハボンディングについて報告された例は少なく、本研究によりその手法の確立を図った。Ge、Si の表面処理条件などを詳細に検討し、ボンディングの最適条件を求めた。また、素子の実現のため、メサエッチングによる素子作製条件を明らかにした。

本研究により 1.55 µm 帯の光に高い受光感度を持ち、かつなだれ増倍過程で 発生する過剰雑音を低減した APD の実現の可能性を明らかにした。

本論文の構成は以下のようになっている。

第1章では、本研究の位置付けを明確にする。

第2章では、受光素子の原理と構造を説明する。

第3章では、Ge/Siの構造設計についての理論検討を行う。

第4章では、確立したGe/Siのウェハボンディングについて述べる。

第5章では、ヘテロ接合Ge/Siの評価と実験による特性の変化について述べる。

第6章では、メサ構造の実現と特性の考察をおこなう。

第7章では、本研究により得た結果を述べる。

# 2章 フォトダイオードおよび APD

本章ではフォトダイオードおよびアバランシフォトダイオードについて概説し、本研究で目指す Si をなだれ増倍層とする APD の意義を明らかにする。まず、PD の原理を説明し、応答速度と暗電流を決める要因についても述べる。次に、APD の動作原理について述べ、そこで問題となる過剰雑音について考察する。

## 2.1 はじめに

一般に、受光素子は光エネルギーを電気エネルギーに変換する素子である。受 光素子では光子(フォトン)のエネルギーを吸収し束縛電子が遷移して自由キャリヤを生成する量子効果を利用した素子が広く使われている。このような効 果は量子効果に基づいており、光電効果と呼ばれている。次の 3 種類に分類される。

光電子放出効果 光電効果 光伝導効果 光起電力効果

光電子放出効果は、光が金属や半導体に照射されたときに真空中に電子が放出される効果であり、光電管、光電子増倍管として実用化されている。

光伝導効果は、光が半導体に照射されたときにキャリヤの増加によりその抵抗が低くなる効果であり、主に赤外線の検出器として用いられている。

光起電力効果は半導体のpn接合やショットキー接合に光を照射し電流または電圧を発生するもので光のエネルギーを電気エネルギーに変換する太陽電池、および光信号を電気信号に変換するフォトダイオードとして用いられている。特にフォトダイオードは、逆方向バイアス電圧を印加し、光電流として信号を取り出すものである。本章では以下フォトダイオードについて詳述する。

#### 2.2 光の吸収

光の光子エネルギーは、光の波長を 、光速を c 、光の振動数を とすれば 次のように表せる。

= c/ =  $\{19.88 \times 10^{-26} [J \cdot m] \}/h [eV]$ =  $1.24 \times 10^{-6} [eV \cdot m]/h [eV] = 1.24/h [\mu m]$  (2.1) と表すことができる。

このような光がバンドギャップエネルギー  $E_g$  の半導体に入射すると、  $h \ge E_g$ 、すなわち光子エネルギーが  $E_g$  より大きいとき、価電子帯から伝導帯 へ電子遷移が起こり、自由電子および正孔が生成される。式 (2.1) から、例えば、バンドギャップエネルギー $E_g$  が 1.24 [eV] の場合、1  $\mu m$  以下の波長の光を 吸収できることになる。

光ファイバ通信で用いられる 1.55 µm の光に対して応答するためには、バンドギャップエネルギーは約 0.8eV 以下である必要がある。

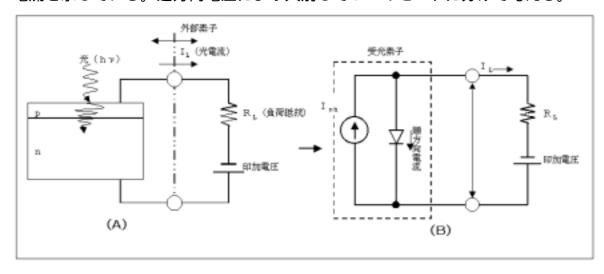

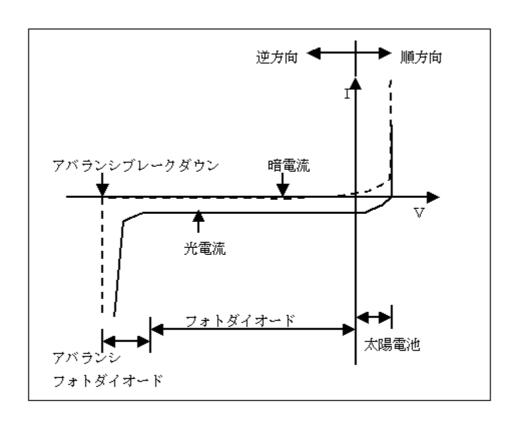

図 2(A)は PD と、接続する外部回路を示したものである。図 2 (B)はその等価回路である。ここで、光電流を Iph とすると、これは電流源と考えることができる。図 3 は p n 接合の順・逆方向バイアスと電圧に対する電流の模式図である。 光入射のない時の暗電流(通常の p n 接合の I-V 特性 ) および、光入射時の光電流を示している。逆方向電圧により大別して 3 つのモードに分けて考える。

図 2 光電流取り出し機構 [11]

図3の(第4象限の)順方向バイアス電圧で逆方向に電流が流れる状態が太陽電池である。逆方向バイアス電圧特性で利用されるのが、第3象限のフォトダイオードモードである。さらに、ブレークダウン電圧近傍の逆方向電圧が印加される状態が後で説明するAPDである。

図 3 受光素子の I-V特性[11]

#### 2.3 太陽電池

太陽電池について簡単に述べる。図4に示されている熱平衡状態のpn接合近傍に光が入ると、n形およびp形領域では電子-正孔対が発生する

いま、発生した少数キャリヤに着目するとp形領域で発生した伝導帯の電子は 平均して拡散長だけ四方に拡散した後、正孔と再結合して消滅する。しかし、 空乏層端から電子の拡散長以内の領域で発生した電子のうちいくつかは、空乏 層端にたどりつき、薄い空乏層内を電界の力を借りてドリフトし、n形領域に たどりつく。同様に、n形領域においても空乏層端からホールの拡散長以内の 領域で発生したホールのいくつかは、空乏層端にたどりつき空乏層内をドリフ トしてp形領域にたどりつく。空乏層内で発生した電子 - 正孔対は分離されて ドリフトし、電子はn形領域に、正孔はp形領域に、それぞれたどりつく。

このように、電子と正孔が逆向きに空乏層内を通過することでn形領域からp 形領域へ向かう逆方向電流が流れることになる。太陽電池モードでは、外部負荷抵抗に発生する光起電圧Vが小さいときは、逆方向電流I」も光起電圧も光量に比例して得られる。しかし、外部付加抵抗に発生する光起電圧Vが大きくな ると、逆方向電流 I 、は光量に比例するほど大きくならず、光起電圧 V は I 、に対して対数的に増加する。

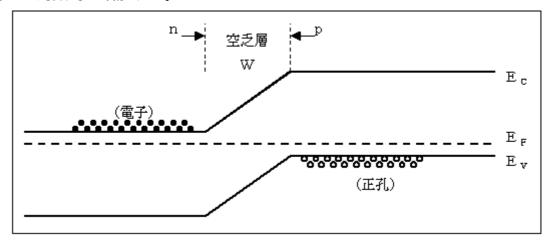

図 4 熱平衡状態のpn接合 [11]

図 5 太陽電池の動作説明図 [11]

## 2.4 フォトダイオード

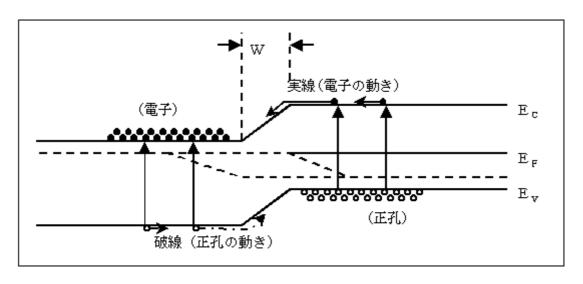

次に、逆方向バイアス電圧を印加した場合、すなわちフォトダイオードの動作について述べる。図6は逆方向バイアス電圧を加えたときのエネルギーバンド構造である。

フォトダイオードモードでは逆バイアスをかけることで空乏層を厚くし、その中でほとんどの光が吸収されるように設計することができる。これにより発生した電子 - 正孔対は空乏層内の電界で加速されドリフト電流として光電流に寄与させることができる。その結果高い光-電気変換効率が得られる。この変換

効率の尺度である量子効率 は次のように定義される。

ここで、入射する光の周波数を とすると、1 光子あたりのエネルギーはh であるから、入射光パワー  $P_{i0}$  に対しては、毎秒  $P_{i0}$  個の光子が入射していることになる。また光電流に寄与するキャリヤ数は光電流  $I_{ph}$  を素電荷 q で割ったものであるので

$$\eta = \frac{I_{ph}/q}{P_{i0}/h} = \frac{I_{ph} \times h}{P_{i0} \times q}$$

(2.2)

と表せる[11]。

図 6 フォトダイオードの基本構造 [11]

さらに受光感度Sを

$$S = \frac{ 光電流}{ 入射光出力} \quad [A/W]$$

と定義すると、 - (2.3)

$$S = \frac{I_{ph}}{P_{i0}} = \frac{q}{h} \eta = \frac{1.6 \times 1 \ 0^{-19} [J]}{h \ [e \ V]} \eta = \frac{1.24}{\lambda [\mu \ m]} \eta$$

となる。後述するように、空乏層は不純物濃度の -  $\frac{1}{2}$ 乗に比例して広がるので、

空乏層幅を低バイアス電圧で広げるためには不純物濃度の低い層を用いる。そのため PIN 構造となり、PIN 構造のフォトダイオードを PIN-フォトダイオード (PIN-PD)と呼ぶ。ここで、「I」はキャリヤ濃度の低い層、i 層(intrinsic layer)総称するもので、特にn 形超低濃度層(n)を層、p 形超低濃度層(p)を層と呼ぶ。

### 2.4.1 応答速度

受光素子の応答速度は以下の3要因によって支配されている[11]。 光生成した少数キャリヤが拡散して空乏層に至る拡散時間 空乏層を走るドリフト時間 静電容量 C と負荷 R による CR 時定数

. 光生成した少数キャリヤが拡散して空乏層に至る拡散時間は、空乏層を十分に広げ、その中でキャリヤを発生させることで十分に抑えることが出来る。

. 空乏層を走るドリフト速度 V<sub>d</sub> (drift velocity) は、低バイアス時には電

界強度 E に比例して増加する。空乏層内をドリフトする電子は、熱振動する格子原子と衝突し散乱される。電界強度 E が大きくなると格子原子と衝突する頻度は増え、最終的には、ほぼ一定の平均ドリフト速度、すなわち飽和速度となる。この飽和速度  $V_{ds}$  (saturation velocity) は、半導体材料によって、および電子・ホールによって変わるが、

$$V_{ds} = 10^6 \sim 10^7 \text{ [ cm/sec ]}$$

(2.4)

であることが知られている[12]。キャリヤが空乏層を走る走行時間 t は空乏層幅 W に比例して長くなる。

. フォトダイオードの応答速度に関連する静電容量は、pn 接合の容量(接合面積と空乏層幅に依存)と、パッケージなどを含めた回路の容量である。これらの容量をCとする。また負荷回路全体の等価抵抗をRとすると、時定数C

R が決まる。これによる遮断周波数 f(CR)(3dB 帯域)は

$$f(CR) = \frac{1}{2 CR}$$

(2.5)

で求めることが出来る。*CR* 時定数を小さくすることによって、遮断周波数の値は大きくなる。高速応答の P D に対して、接合容量を小さくするために PIN 構造としたり、あるいは逆バイアスを大きくして、空乏層を広げることが出来るように設計する。しかし、PD の容量を小さくする最も重要な要因は接合面積(すなわち受光面積)であり、必要に応じて出来るだけ小さな面積とするように設計される。

なお、上記 と においては次のようなトレード・オフの関係になるため両者 がバランスすることが望ましい。

| 応答速度要因                  | バイアス電圧 | 空乏層幅 | 応答速度 |

|-------------------------|--------|------|------|

| 空乏層を走るドリフト時間            | 大きくする  | 広がる  | 長くなる |

| 静電容量 C と負荷 R による CR 時定数 | 大きくする  | 広がる  | 短くなる |

#### 2.4.2 暗電流

光が入射しないとき、逆方向バイアス電圧に対して流れる電流を受光素子においては暗電流と呼ぶ。後述する APD においても暗電流は増倍され雑音の発生源となることがあるので小さいほど望ましい。この暗電流の原因としては

- . 拡散電流

- . 発生・再結合電流

- . トンネル電流

- . 表面リーク電流

#### の4つがあげられる。

まず、暗電流の主因となるのが拡散電流である。拡散電流は p-n 接合やショットキー接合における逆方向飽和電流であり、半導体の特性パラメータで決まり、さらに接合面積に比例して増加する。

発生・再結合電流は空乏層内にあるトラップ準位を介して、発生・再結合する電子・ホールによる電流で、結晶欠陥や、プロセスを清浄化することで抑えることが出来るとされている[11]。

トンネル電流は、高電界が印加されバンドが急峻になったとき、伝導帯から価電子帯へあるいは、その反対方向へ電子がエネルギー変化なしに遷移するために起こる。バンドギャップの小さい半導体の p-n 接合で起こりやすい。 InGaAs が実現できない原因とされ、このため InP をなだれ増倍層とする APD が

用いられる構造となった。なお、本研究では Si をなだれ増倍層とするためトンネル電流を無視することが出来る。

表面リーク電流は表面に露出する p-n 接合を介して流れる電流成分である。 本研究で実現する試料の暗電流の大部分はこのようなリーク電流であると考えられ、これについては 5.3 節でも述べるように、表面の清浄化や、パッシベーションにより改善することができると考えている。

## 2.5 アバランシフォトダイオード(APD)

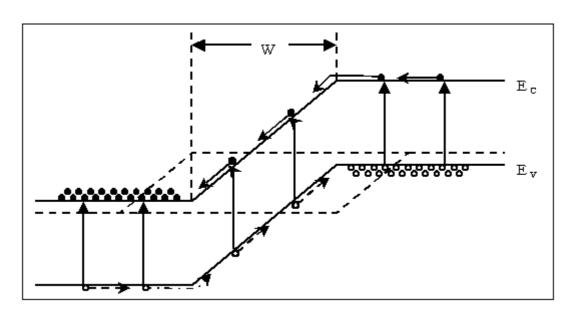

次に、アバランシフォトダイオードの動作原理、および増倍雑音について述べる。図7はなだれ降伏電圧近傍までバイアス電圧を加えたときのエネルギーバンド構造である。p-n接合に印加する逆方向バイアス電圧を増加させると、空乏層をドリフトする電子は格子原子に衝突し散乱される。電界強度 E が大きくなると格子原子と衝突する頻度は増えドリフト速度はほぼ一定の値(飽和速度 V ds)となる。さらに、電界強度を増すと、一部のキャリヤのエネルギーが大きくなり、格子原子との衝突による衝突電離(impact ionization)が起こる。これは格子原子と衝突した際に、格子原子に束縛されている価電子を伝導帯に励起して、電子・正孔対を作る現象である。さらに新しく発生した電子・正孔対が電界で加速されてまた別の電子-正孔対を発生させる。このような過程を繰り返すことによって電流が急激に増大する。この現象をアバランシブレークダウン(なだれ降伏; avalanche breakdown)という。アバランシ増倍(なだれ増倍; avalanche multiplication)は、光電流に対してこの現象を利用し、出力光電流を増幅するものである。アバランシ増倍を利用したフォトダイオードをアバランシフォトダイオード(APD)という。

図 7 アバランシフォトダイオードの基本構造 [11]

#### 2.5.1 過剰雑音

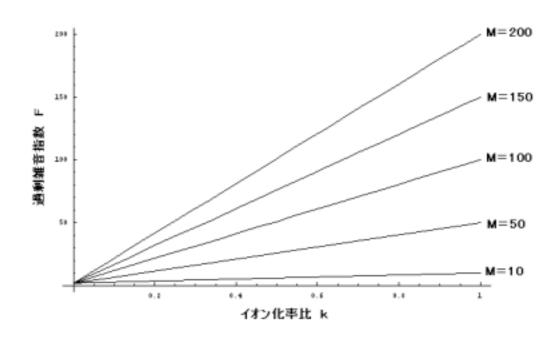

なだれ増倍はランダムな過程であり、このため過剰な雑音(excess noise)が発生し、APD の主要な雑音源となる。APD に $_{PO}$ の光電流が流れた時アバランシ増幅されて電流は $_{PO}$ M となる。M を増倍率と呼ぶ。この時、雑音電力密度  $\left\langle \bar{\mathbf{i}} \right\rangle^2$  は  $\left\langle \bar{\mathbf{i}} \right\rangle^2$  = 2  $_{PO}$ M $^2$ F(M) と表される。過剰雑音は過剰雑音指数 F(M)で与えられ、次式で表されることが知られている[4]。

$$F = M \left\{ 1 - \left(1 - k\right) \frac{(M - 1)^2}{M^2} \right\}$$

- (2.6)

ここで、k はイオン化率比であり を電子のイオン化率、 を正孔のイオン化率 とすると、電子注入の場合 k=-、ホール注入の場合 k=-である。式 (2.6) を 用いて、図 8 に各増倍率 M による過剰雑音指数 F とイオン化率 k の関係を示した。図 8 から増倍率 M が大きくなるほど過剰雑音に対するイオン化率の影響が

大きくなることが分かる。イオン化率k が 0 に近づくと $F \simeq 2 - \frac{1}{M}$  と近似でき、十分に増倍率が大きくなると、理想値 $F \simeq 2$  となる。

図 8 各増倍率における過剰雑音係数

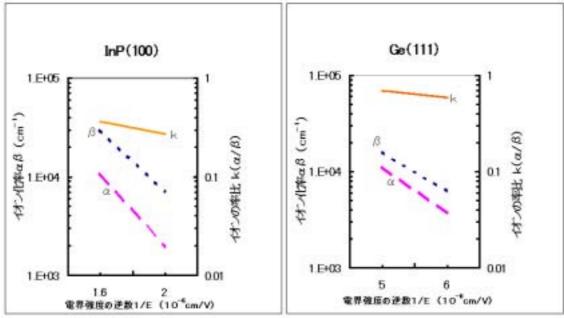

図 9 にこれまで知られている半導体におけるイオン化率を示した。 ${f Si}$  のイオン化率比- が最も小さいとされている。 ${f Si}$  の場合  $k\simeq 0.02\sim 0.1$  となり他の半導体と比べ最小の値となる。そのため  ${f Si}$  をなだれ増倍層とするのが有効である。

図 9 各半導体におけるイオン化率、イオン化率比 (Si[2]、InP[3]、Ge[13])

## 2.6 本章のまとめ

本章ではフォトダイオードおよびアバランシフォトダイオードの動作について述べた。

APDで問題となる過剰雑音は衝突イオン化率に依存し、過剰雑音指数は電子と正孔のイオン化率比に依存する。現在知られている半導体結晶では Si のイオン化率比は  $0.02 \sim 0.1$  と最も小さい。このことから、なだれ増倍層に Si を用いることが有効であることを述べた。

## 第3章 Ge/Si-APD の基本構造と設計

本章では本研究で実現を目指す p-Ge/pn-Si-APD 構造について述べ、PD として必要な膜厚・不純物濃度など、Ge および Si についての必要なパラメータを求める。

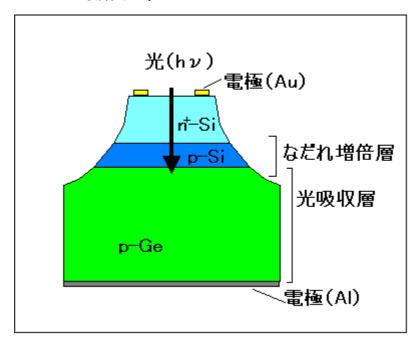

### 3.1 Ge/Si-APD の構造

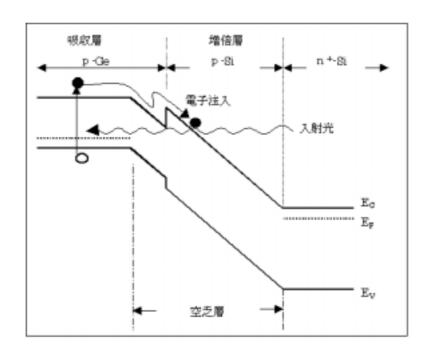

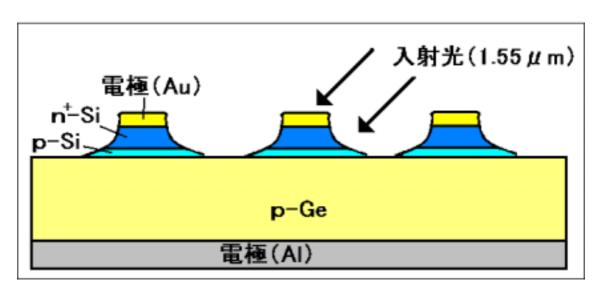

本研究で実現を目指している Ge/Si APD の構造を図 10 に示す。この構造では、1.55 μm の光を Si 側から入射し、Ge 層で吸収される。吸収によりキャリヤが発生し、ヘテロ接合を越えて光電流を取り出すことができる。p-Si に十分に高い電界が印加されていると、光電流はなだれ現象により増倍される。このように、光吸収となだれ増倍を起こす領域を分離している構造を Separaed Absorption and Multiplication Region の頭文字をとって SAM 構造と呼び、または SAM-APD と呼ばれる。図 10 に示すようにメサ型とすることで pn 接合端面での局所的なだれ降伏を防止すると APD として動作する。

図 10 Ge/Si アバランシフォトダイオード構造 [14]

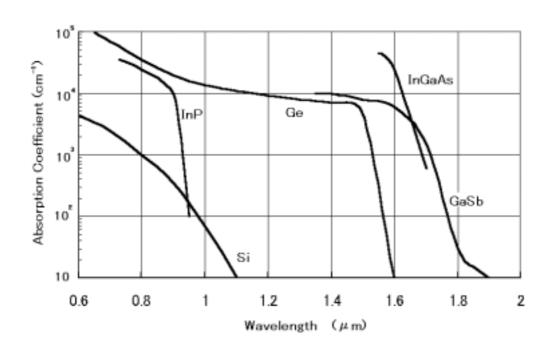

#### 3.2 吸収係数

ここでは Ge で吸収される光の量について考察する。 光吸収の大きさは光吸収

係数  $_0$  (absorption coefficient)で表せる。2.2 節で述べたように半導体のバンドギャップに対応する光の波長は  $\left[\mu\,m\right] = \frac{1.24}{E_g\left[e\,V\right]}$ で決まる。しかし、Ge の

ような間接遷移半導体は光吸収にフォノンの吸収・放出過程が伴う。よって直接半導体に比べ光吸収の遷移確率は低い。その結果直接遷移半導体と比べ、吸収端からの吸収係数の立ちあがりは緩やかである。 $E_g$  近傍の光子エネルギーEに対して、吸収係数。は間接遷移型では。  $(E-E_g)^2$ で表せる事が知られている。また光が入ることの出来る深さの目安として L は浸透長 (light penetration depth)といわれ、 $L=\frac{1}{0}$ となる。媒質中を L 進んだ光は 63%  $(1-e^1)$  吸収され、 $37\%(e^1)$ に減少する。

図11は現在報告されている半導体吸収係数の波長に対する依存性を示したものである。図より、Geの波長 1.55 µm の光に対する吸収係数は約 10³ (cm ¹)である。吸収される光の量は 100%に近いほど良いのだが、光は対数的に減衰するため空乏層幅とのバランスを考えなければならない。ここでは適当な値として、光が 90%吸収される場合を考える。

$$1 - e^{x} = 0.9$$

$e^{x} = 0.1$  - (3.1)

$X = 2.3$

つまり浸透長 10(μm)の 2.3 倍、23μm、Ge 基板中を光が進むことになる。

しかし、資料によっては Eg = 0.65 程度とされており、その場合吸収端は 1.91  $\mu m$  となる[1]。実際に、Ge-PD あるいは Ge-APD は市販されているが、その測定結果やカタログデータから、 $1.55~\mu m$  の光に対して十分な感度があり、Ge の吸収端は図 11 よりも長波長側にあると思われる。

図 11 半導体の吸収係数 [15~17]

## 3.3 基板材料

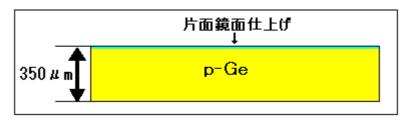

本研究で用いた基板の仕様について述べる。 基板材料としては p-Ge と p-n<sup>+</sup>Si を用いた。 p-Ge 基板の仕様は以下の通りである。

図 12 p-Ge基板

製法: Cz 法

不純物:Boron 厚み:350 [μm]

比抵抗:0.1~0.5 [·cm]

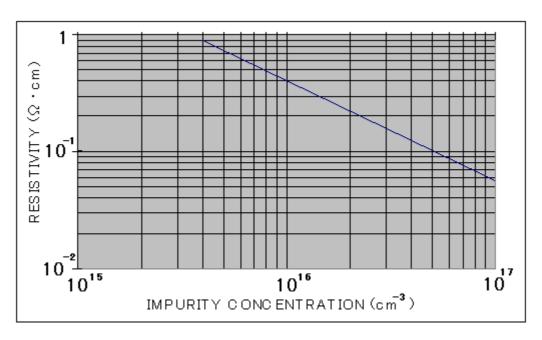

3.2 節で述べたように、Ge に伸びる空乏層幅は数 μm 以上必要であり、P型不 純物濃度はできるだけ低いことが望ましい。しかし、市販品として比較的容易 に入手し得る Ge 結晶として、このような仕様とした。ここで p-Ge の非抵抗値 と不純物濃度の関係は温度 3 0 0 Kにおいて、図 13 に示すようになる。

図 13 p-Geの比抵抗値と不純物濃度の関係 [18~20]

この図と p-Ge の比抵抗値を用いて、 p-Ge の不純物濃度は、 $7.5 \times 10^{15} \sim 5 \times 10^{16}$  (cm<sup>-3</sup>) であることが分かる。

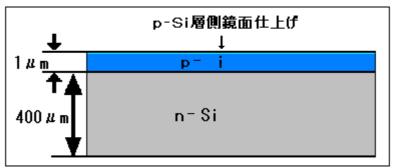

pn<sup>+</sup>-Si 基板の仕様は以下の通りである。

図 14 pn-Si基板

製法:n<sup>+</sup>Si 基板上にp層をエピ成長

n⁺-Si

不純物:Sb

厚み:400 [μm]

比抵抗:0.010~0.015 [·cm]

p-Si

不純物:Boron

厚み:1 [μm]

比抵抗:0.320~0.480 [·cm]

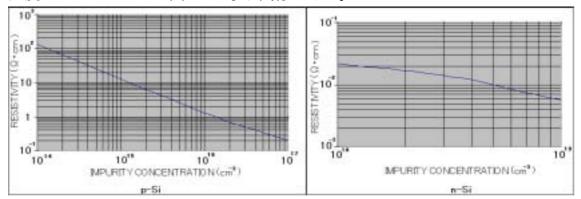

3.5 節で述べるように、p-Si 層は完全に空乏し、さらに降伏電圧以下で空乏はヘテロ接合を越えて Ge に十分伸びる必要がある。p-Si の比抵抗値は上記仕様の 2 倍以上であることが望ましい。ここでp-Si、n-Si の比抵抗値と不純物濃度は、温度 3 0 0 K において図 15 が示す関係になる。

図 15 Si の比抵抗値と不純物濃度の関係 [20]

この図 15 と p -Si、 n -Si のそれぞれの比抵抗値を用いて p -Si の不純物濃度は  $3.2\times10^{16}\sim5.4\times10^{16}$  ( cm $^{-3}$  ) n -Si の不純物濃度は  $2.5\times10^{18}\sim5\times10^{18}$  ( cm $^{-3}$  ) であることが分かる。

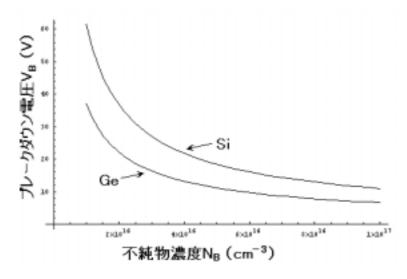

## 3.4 アバランシブレークダウン電圧

アバランシフォトダイオードのpn接合を片側階段型接合として、なだれ降伏電圧 $V_B$ を見積もる。 $V_B$ における最大電界強度を $E_{max}$ とすれば、ブレークダウン電圧 $V_B$ は次式で近似されることが知られている[21]。

$$V_{B}[V] = \frac{E_{max}W}{2} = \frac{\kappa \epsilon_{0} E_{max}^{2}}{2q N_{B}}$$

$$\simeq 60 \left(\frac{E_{g}[eV]}{1.1}\right)^{\frac{3}{2}} \left(\frac{10^{16}}{N_{B}[cm^{-3}]}\right)^{\frac{3}{4}}$$

(3.2)

図 16 不純物濃度によるブレークダウン電圧

ここで  $N_B$  は pn 接合の濃度が低い基板側の不純物濃度、 $E_g$  は基板材料のバンドギャップである。また、式 (3.2) を図に表したものが、図 16 である。今回使用した pn シリコン基板の低濃度側を  $5\times 10^{16}$   $(cm^{-3})$  とすると、式から、 $V_B$  は 18.4V であると、予想される。pn Si のみでの実測値では 14~1~6~V 程度となった (カーブトレーサにて測定) のでこの式は、それなりに目安になるものであるといえる。そのときの測定値を図 16 に示す。

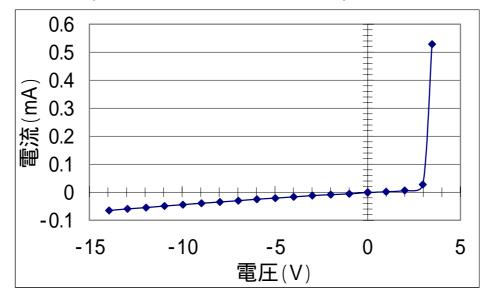

図 17 pn-Siの I-V 特性

### 3.5 空乡層幅

ここでは空乏層と不純物濃度の関係を述べ、使用した試料について計算する。

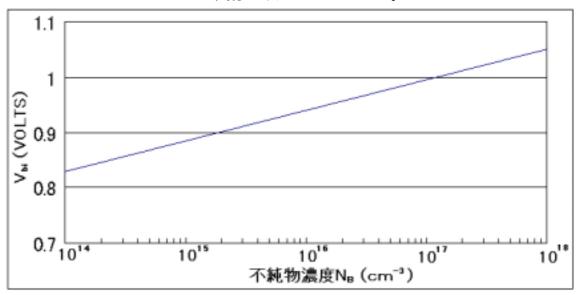

#### 3.5.1 拡散電圧 VD

空乏層幅を決めるパラメータとして拡散電圧  $V_D$  がある。このパラメータは基板材料とその不純物濃度で決まり、次式で表せる。

$$V_{D} = -\frac{kT}{q} \ln \left( \frac{p_{p0} n_{n0}}{n_{i}^{2}} \right)$$

(3.3)

ここで、 ${\bf k}$  はボルツマン定数、 ${\bf p}_{p0}$  は  ${\bf p}$  形領域中のホール濃度、 ${\bf n}_{n0}$  は ${\bf n}$  形領域中の電子濃度、 ${\bf n}_i$  は基板材料の真性キャリヤ濃度を表す。この式から今回の ${\bf p}$   ${\bf n}$  -Si では  ${\bf 0}$ .91 V ${\bf p}$  0.94 であることが分かる。図 18 は低濃度側不純物濃度とビルトインポテンシャルの関係を表したものである。

図 18 n <sup>+</sup>-Si/p-Si の不純物濃度とビルトインポテンシャル[22]

図 18 から、ビルトインポテンシャルVDはバンドギャップ以上の電圧にはならず、幅も 0.3V 以下となり、大きな変動がないため、今回求めている他のパラメータと比較して余り気にする必要はないことが分かる。

#### 3.5.2 空乏層幅

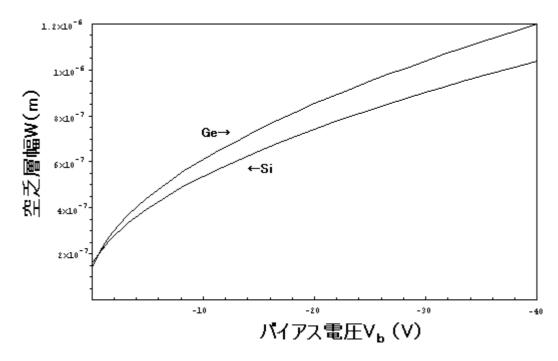

空乏層幅は、を半導体の比誘電率とすると、次の式で与えられる。

$$W = \left[ -\frac{2 \ \varepsilon_0}{q} \left( \frac{1}{N_D} + \frac{1}{N_A} \right) (V_D + V_b) \right]^{1/2}$$

(3.4)

図 19 に今回の条件に合わせた不純物濃度  $N_B = 5 \times 10^{16} cm^{-3}$ 、Si のビルトインポテンシャル  $V_D = -0.98$  として、バイアス電圧と空乏層幅の関係を表した。式 (3.4) から基板の不純物濃度に大きな差があるときは、空乏層幅Wは低濃度基板側の不純物濃度に大きく依存し、今回の pn-Si では空乏層を Ge 層まで広げるため、1 pmとするには 23.1  $V_b$  39.7 となることがわかる。

図 19 実験試料におけるバイアス電圧と空乏層幅

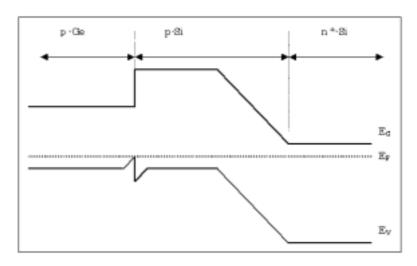

## 3.7 ヘテロ接合

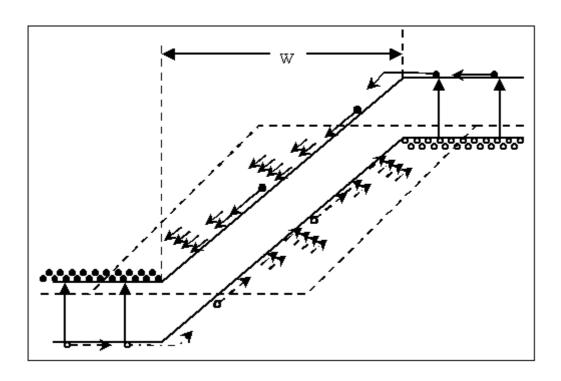

実際の素子では空乏層が Ge まで広がっていてもキャリヤが流れない場合がある。図 20 に p-Ge/p n-Si ヘテロ接合の熱平衡状態エネルギー構造を示す。図に示すようにヘテロ界面にエネルギー障壁(ノッチ)ができ、キャリヤの流れを妨げている。図 21 は逆方向バイアスを印加した時のバンド構造である。逆方向バイアスを高くすることで、発生したキャリヤがヘテロ界面の障壁を乗り越えると光電流が流れる。ここで、重要なことはキャリアがヘテロ障壁を乗り越えるため大きな逆バイアスと空乏層が十分に光吸収層に入り込んでいることが重要である。

図 20 熱平衡状態でのバンド構造 [8]

図 21 逆方向バイアス印加時のバンド構造 [8]

## 3.8 本章のまとめ

本章では理論式から、今回使用した基板材料について予想される特性を計算 してみた。手持ちのデータから得た結果は、

1. p-Si の不純物濃度は約  $4 \times 10^{16} cm^{-3}$ 、n-Si の不純物濃度は約  $4 \times 10^{18} cm^{-3}$ 、Ge の不純物濃度は約  $1.5 \times 10^{16} cm^{-3}$ である。

- 2.今回用いた資料では Ge のバンドギャップエネルギーEg は 0.8eV であり、その場合の吸収端が  $1.55~\mu m$  であった。しかし、他の資料から Eg は 0.65eV である可能性もあり、その場合の吸収端は  $1.91~\mu m$  という光通信に用いるのに十分な値となる。

- 3. pn-Si のブレークダウン電圧は 18.4V である。

- 4.今回用いた pn-Si では、p-Si 内に空乏層幅  $1 \mu m$  広がり光電流が発生するために必要な電圧は -23V 以上である。

今回用いたデータから今回使用したサンプルでは予定していた不純物濃度より p-Si の不純物濃度が若干高いため、p-Ge のキャリヤの発生はあまり期待できないことが分かった。しかし、図 1 9 ~ 2 1より p-Si 層を十分薄くすることでp-Ge から発生する少数キャリヤを利用し、アバランシ増幅できる可能性があることが分かる。

## 第4章 ウェハボンディング

本章ではp n - Si/p - GeAPD に向けて、ウェハボンディングを行い、ボンディング最適条件を求めた結果を示す。また、p - Ge/p - Ge、p - Ge/n - Si、p - Ge/p - Si についてのボンディングも成功した。

Si の格子定数は 5.43 ( ) Ge が 5.66 ( ) である[23]。このため、Si 上に Ge をエピタキシャル成長させるのは格子整合の面から難しいとされている。そこで、ウェハボンディングという手法を用いて素子を作製することにした。

## 4.1 ウェハボンディング

ウェハボンディングは確立された手法である。原理は洗浄した基板に OH 基を付け接着後加熱などにより取り除く手法である。どの素材にどの薬品が合うか、どの処理が必要かは、ボンディングする試料ごとに変わってくる。本来なら素材ごとの化学反応を知っておき、科学的知識から薬品を選択するのが効率的方法になりえるはずだが、実際には反応時間や、温度に依存する部分が大きく、理論で割り切ることが難しい現象である。本章の意義は、ボンディングできる素材を増やしていくことで、それを利用した幅広い研究が可能となり、同時にその他の素材のボンディングにも何らかの応用がきくということである。

水中でのウェハボンディングの基本的手順は次の通りである。基板をあらゆる方法で洗浄し、水中での反応性を高めるため、OH 基を各基板につけることで、互いの基板が OH 基を介して接着力を持つ、接着した基板から OH 基を取り除くことで両基板間の空間を最小にすることが出来る。その結果距離の 4 乗に比例するファンデルワールス力により、接着される。

## 4.2 ボンディングプロセスと成功率の改善

実際行った実験工程は次の通りである。

<手法1>

洗浄

(樹脂、塵、皮脂)

- 1. アセトン 10min

- 2. メタノール 5min

$3.H_2O$  5 min

(酸化膜、金属片)

- 4.B-HF 5min

- 5. HF: H<sub>2</sub>O = 1:1 5min 基板活性化

- 6. H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O = 3:1:1 10min \* 4 ~ 6後に H<sub>2</sub>O リンスが入る。

- 7. H<sub>2</sub>O 中でボンディング

- $8.N_2$   $\overline{D}$

- 9. ホットプレート (HP) で加熱 160 1 h

以上の条件で、夏季には8割以上の成功率になっていたのだが、冬期には成功率は1割程度になった。下の表は上記の手法で行ったボンディングの成功率を季節ごとで分けたものである。

| 季節  | 春(4~6月) | 夏(7~9月) | 秋(10~12月) | 冬(1~3月) |

|-----|---------|---------|-----------|---------|

| 成功率 | 約 50%   | 約 90%   | 約 40%     | 約 10%   |

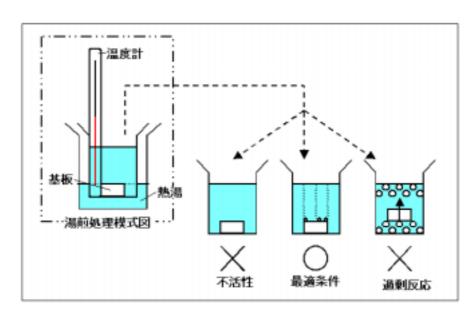

図のように気温が高い夏季は成功率が上がり、気温が低い冬期はほとんど成功しなくなった。そのために着目したのが、気温(温度)による変化である。薬品は基本的に高温で活性になり、低温で不活性になるものが多い。まず、硫酸処理(H2SO4+H2O2+H2O)の温度を変化させた。ビーカー内のお湯をホットプレートで沸騰させ湯煎する方法を取った。その結果、冬期にもかかわらず27個連続成功し、高い成功率となった。しかし、残念ながらその時の詳しい温度変化は記録しておらず、必ずしも再現性があるとは言えない。当時の実験内容を再現して硫酸処理の温度変化を調べたところ30~45 程度となっていた。逆に、硫酸を湯煎しても失敗したケースは大量の大粒の泡が発生中に処理を行ったときである。例えば、70 以上の高温で処理を行った場合、大粒で多量の泡が発生した。

多量の泡が発生した場合でも、その中で処理を行わずに、時間をおいて反応がおさまってから処理を行うと比較的良い結果を得られた。多量の泡の中処理を行うと p-Ge に対し過剰反応が起こり表面に傷、または白い筋がつくのがボンディングの成功しない大きな理由となる。この時、同条件で処理を行った Si 基板に傷はなかった。

白い筋がつく原因として、酸化膜の除去が不完全であることが考えられる。 酸化膜による原因のみに原因があると仮定して、以下の条件で実験をおこなった。

- ·B-HF を湯煎で 30 程度にし、10 分処理を行った。

- ・70 以上の条件で硫酸処理を行った

その他の条件は<手法1>と同様である。その結果70度処理中多量の泡が発生し、表面に多くの傷がついた。この事から酸化膜以外の影響もあり表面が荒れていることが証明できた。

今回は硫酸のみの温度変化で十分に成功率を改善できたので確認はしていないが、実際には の基板活性化についても反応が悪くなっている(洗浄・エッチレートが落ちている)はずである。実験的に気温が5 以下程度の時は洗浄処理も湯煎して行わなければ失敗が多いことが確かめられた。

湿度に関しても、同様の理由で確認していない。

以上の結果をまとめると  $H_2SO_4:H_2O_2:H_2O$  の最適条件は 9m1:3m1:3m1、組成してから 30 分程度おいたもの、処理温度は  $30\sim45$  程度、時間は  $10\pm1$  分となった。

#### <手法2>

手法 1 + 基板活性化最適条件

- H<sub>2</sub>SO<sub>4</sub>... 9 m 1

- $H_2O_2...3 m 1$

- H<sub>2</sub>O...3m 1

- · 処理時間 10 ± 1 min

- · 処理温度 35~45 程度

- ・ 組成後、多量の泡が発生した場合は、30分程度おいたもの

実験的に全く泡が発生しない場合は、反応が少なすぎ、基板に小粒の泡が適量付着した場合が最適で、大粒の泡で基板が浮き上がったりする場合に過剰反応で成功率が下がることがわかる。過剰反応を起こしたときは Ge 基盤の鏡面は白くにごり薄い傷がつき、裏面は黒くにごる。

図 22 硫酸系処理図と最適条件

### 4.3 前処理による特性の改善

B-HF、HF +  $H_2O$  の処理時間により Si 鏡面側の膜厚は、若干薄くなる。今回の p-Si の膜厚は 1  $\mu m$  のため遅いエッチャントでも十分危険である。そのため、ボンディングが失敗した p n-Si 基板で特性を測定し、整流性が見られることを確認した。

さらに、設計の段階で p-Si の膜厚を理想値にした場合、酸化膜除去のため、必要以上に p-Si 層が削れることは好ましくない。このため膜圧の誤差を改善するため、次の実験を行った。

#### 実験として

<手法3>B-HF 5 min のみで<手法2>を行う場合

< 手法  $4 > HF: H_2O = 1:1$  5min のみで < 手法 2 > を行う場合についてそれぞれ行ったところ、両手法でボンディングを成功することができた。

B-HF、HF+H<sub>2</sub>O はほとんど同じ意味合いで行なわれている処理である。よって一方を省略できると考えられる。B-HF は業者から購入した物で濃度は一定に出来る。しかし、HF+H<sub>2</sub>O については作業者に依存し、何度も正確に組成するのは不可能である。人という不確定要素を出来るだけ除くのであればB-HFを残す方が賢明である。今回、両手法とも実験したのは応用の幅を広げるためである。

## 4.4 ボンディング結果

経験的に、<手法3>、<手法4>に比べ<手法2>の方が超音波洗浄に耐える強力な素子を作製できる可能性が高い。この手法をもちいてボンディングに成功した材料は次の通りである。

- p-Ge/p-Ge

- p-Ge/n-Si

- · p-Ge/p-Si > p-Ge/pn-Si(p側)

ボンディングの根本的なテクニックとして

- 1. 基板が完全に洗浄されていること

- 2. 反応速度、時間共に最適な活性化処理が行なわれていること

- 3. 同じ薬品でも使用条件(時間・温度)によって大きく結果が 異なること

が挙げられる。この条件を抑えればボンディングの成功率は確実に上がる。特に、同じ薬品でも使用条件によって大きく結果が異なるので、時間・温度を上手に調節し、基板がいたまない程度に1,2の条件を満たすことが大切である。

## 4.5 ホットプレート (HP)

HP 時間は  $70 \pm 5 \min$ 、設定温度は 160 である。現実の実験の場合、気温によって 16 に達するまでの時間が異なるため若干アニール時間は違ってくるが、 160 で 60 分加熱されるように設定する。

加熱中の重りは図のものを使用している。重さは 160 g である。今回の実験では重さにはこだわらず  $3\sim5$  の試料を同時に加熱したので、1 試料あたりの負荷は  $32\sim53$  g である。圧力は小さい Si 基板面積で決まり、Si 基板面積は 16 mm  $^2$  なので圧力は  $2\sim3.3$  g / ( mm  $^2$  ) である。

図 23 ホットプレートと重り

### 4.6 アニール

アニールは $H_2$ 中で600、1時間の条件で行った。アニール中には925gの重りを用い、 $11.6 \sim 19.3$ g/(mm²)の圧力を加えながら行った。アニール温度が高いほどボンディングが強力になるといわれている。しかし、両素材の熱膨張係数の違いが大きければ加熱時にかかる応力が大きくなる。つまり、熱膨張に耐える範囲で高い温度で加熱するのが良いといえる。Si の熱膨張係数は4.2  $\times 10^{-6}$  (/ ) Ge は  $5.5 \times 10^{-6}$  であるので、両者の差は  $1.3 \times 10^{-6}$  である。今回の実験ではアニールによるボンディングの失敗はほとんどなかったので、熱膨張係数差が  $1.3 \times 10^{-6}$  の場合はアニール温度 600 で問題ないといえる。

## 4.7 本章のまとめ

本章ではp-Ge/pn-SiAPD の作製を目的として、Ge/Si のボンディングを行った結果を述べた。

- ・ まずバルク基板を用いp-Ge/p-Ge、p-Ge/n-Si、p-Ge/p-Si、のボンディングに成功し、n-Si 基板にp層をエピ成長させたpn-Siを用い、pn-Si/p-Geのボンディングに成功した。

- ・ ボンディングの成功率を高めるため硫酸処理の最適温度・最適時間 を求め p n -Si/p-Ge において 9 割近いボンディング成功率を得た。

- ・ 工程の簡略化に成功し、手法 2 と同様に高いボンディング成功率を得た。

## 第5章 素子製作

本研究で実現を目指す Ge/Si-APD 素子製作工程は大きく分けて5つになる。

- 1. ウェハボンディング

- 2. 研磨

- 3. エッチング

- 4. 電極づけ

- 5. メサ型エッチング

本章ではこれらの工程について検討した結果を述べる。各工程で終了ごとに 電気特性を測定し、その結果を検討した。

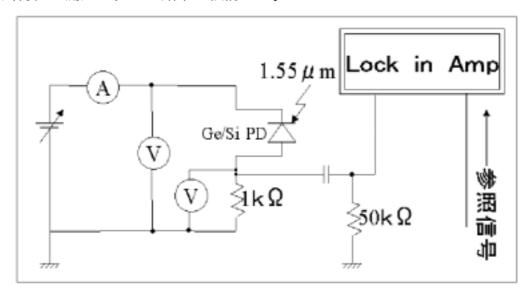

図 24 測定回路図

測定回路は図24のものを使用した。今回の測定では光電流が雑音との区別がつかないほど微弱であったため、ロックインアンプは用いなかったが光電流を確認するためには有効な手段である。

## 5.1 ウェハボンディング

4章で述べたウェハボンディングにより接合を形成した試料について、カーブトレーサーを用いて電流・電圧特性の測定を行った。作製した 30 個の試料の測定を行い、その個数を表に示す。ここで最大電流とは、逆方向暗電流 0.1 m A に達するまでのおおよその電圧である。3.5 節でも述べたように、出来るだけ

高い電圧をかけられることが必要となる。

| 最大電圧(V) | -20 | -15 | -10 | -5 | 0 |

|---------|-----|-----|-----|----|---|

| 個数(個)   | 3   | 6   | 13  | 6  | 2 |

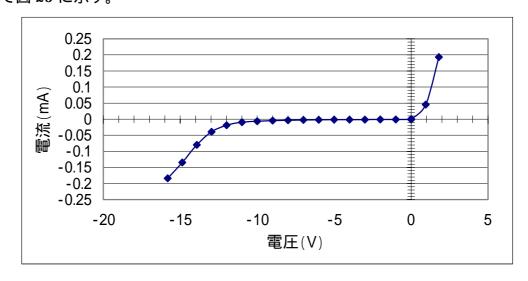

逆方向電流は、不純物濃度などで決まる逆方向飽和電流でありなだれ降伏電圧で急激に増大する(2.2 節参照)。しかし、実際作製した試料では大きな暗電流が流れ、逆方向電流の増加が緩やかである。これは後のエッチングの節で述べるリーク電流が大きな原因である。最も個数の多かった-10V のものを一例として図 25 に示す。

図 25 ボンディングによる試料の I-V 特性

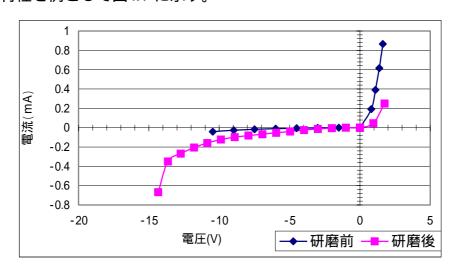

#### 5.2 研磨

次の工程はp-Geとn+-Si層の研磨である。研磨は人工的につけられた保護用酸化膜の除去、表面仕上げは鏡面研磨とし光が入射する時、表面での散乱を少なくすること、および電極づけのため行った。また、研磨に耐えれることで、接着力の確認を行うことができる。

#800 (数字が大きい程細かい)の研磨を行う。 - > 厚さ 100 μm 以上の研磨

#1500 の研磨を行う > 厚さ 100 μm 以下の微調整で基板をより平面に近づける

純水でジグを超音波洗浄し、鏡面研磨で仕上げる。 > 数 μm 程度しか削れない

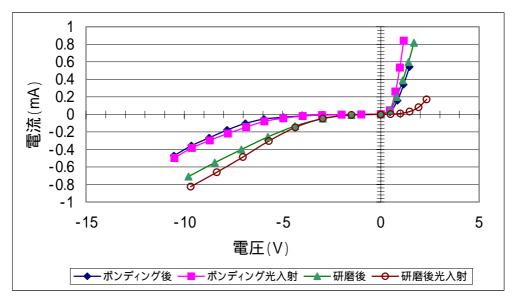

今回作製した素子でははっきりとした光電流の確認は出来なかった。 確実な光電流とは言えないが、微弱な光電流が見られた試料の一例を図 26 に 示す。

図 26 (波長 1.55 µm に対する)研磨による影響 1

研磨することで、研磨された金属片や研磨ジグに試料を固定するためのワックスが基板に付着する。研磨後の超音波洗浄でボンディングがはがれるケースが多いため、洗浄は撹拌だけで行った。その後温水で基板洗浄を行った試料の電流-電圧特性を例として図 27 に示す。

図 27 研磨による影響 2

図をみて分かるように研磨工程により、接合端面が汚染され、暗電流が増加している。これは予想されることである。

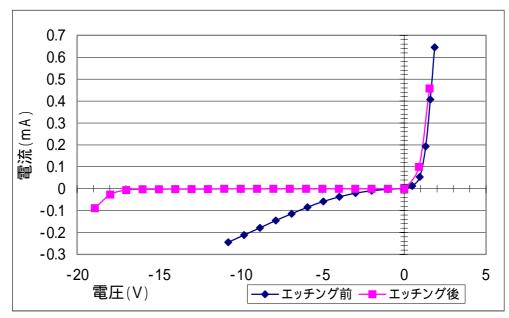

#### 5.3 エッチング

つぎにボンディングされたウェハにおいて、pn接合端面の汚染を取り除くためにエッチングした。これにより暗電流を抑えることが出来ると期待できる。表面のエッチングには次の2種のエッチャントにより順次行った。

$1. HF : H_2O = 10 m 1 : 10 m 1 ... 3 min$

2. HF:  $HNO_3$ :  $CH_3COOH = 2 m l : 1 5 m l : 5 m l ... 5 min$

図 28 エッチングによる影響

このエッチング後の試料の電流・電圧特性を図 28 に示す。図のように暗電流を大幅に減らすことができる。10V での電流は-0.2mA が-0.45  $\mu$ A に減少している。ボンディング直後は試料ごとに暗電流にばらつきがあるが、エッチング処理を行った試料は 1mA での電圧が -15 -20V 程度になった。ウェハボンディング後の状態でのp n 接合端面のエッチングは暗電流を減少し、高電圧を印加するのに必要な工程であるといえる。

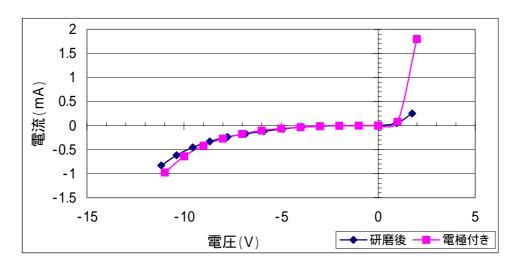

# 5.4 電極付け

電極付けは、特に不純物濃度の低いp-Ge に対してオーム性電極とするのに必要である。n-Si に Au、p-Ge には Al を用いることした。金属蒸着は抵抗加熱装置を用いて行った。蒸着後、400 でアロイ(合金化)を行った。

研磨後特性の悪化した試料に電極付けを行ったところ次の結果となった。

図 29 電極の影響

電極付けにより、順方向特性は改善された。これは不純物濃度の低いp-Ge側が接触抵抗の影響を受けやすいためである。

#### 5.5 メサ型エッチング

メサ型エッチングはリーク電流を少なくするだけではなく、面積を小さくすることで暗電流も抑えることが出来る。詳細については次章で述べる。

### 5.6 本章のまとめ

本章ではウェハボンディング後の試料の処理方法について検討した結果を述べた。また、各工程での素子の電流-電圧特性を測定し、一定の暗電流となる逆方向バイアス電圧が試料の良否の評価に有用あることを述べた。各工程毎に得られた結果をまとめる。

- 1.エッチングにより p n 接合端面の汚染などによるリーク電流を抑えることができた。

- 2.電極形成により順方向電流の立ち上り電圧を予想される値(~1V)に出来ることを確認した。

以上のことからボンディング後、素子の I-V が悪い場合もメサエッチングまでの工程で改善できることが明らかになった。特に、エッチングによる素子への影響は大きいことを明らかにした。

# 第6章 特性の改善

本章では、Ge/Si 接合を APD として機能させるため、メサ型構造の実現を 試みた。また、受光感度改善のため検討を行った。

# 6.1 メサ型エッチング

ボンディング後の試料を、メサ型構造として最終の PD または APD 構造とするために次のような工程手順を提案した。

# 1.研磨(Si->100 µm 以下・鏡面)

Si 層を  $100~\mu m$  以下とした。理由は  $100~\mu m$  程度が研磨によって調節し易い適当な値であること、メサ型エッチングを行う際に Si エッチャントに Ge も削られてしまうためである。鏡面研磨にしたのは、入射光の散乱を抑えるためである。

# 2. 電極づけ(アロイ)

素子をオーミックにするため、n-Siに Au、p-Ge に Al を蒸着し、アロイを行った。

#### 3. メサ型エッチング

Au はメサ型エッチングする際のマスクとして用い、そのまま電極として使用する。Al 電極は Si エッチャントから Ge を保護する。リーク電流を減少させると同時に面積を小さくすることでより暗電流が小さくなる。

図 30 p-Ge/pn-Si メサ型構造

この工程を行うためには、Si の深いエッチングが不可欠である。フォトリソ

用のレジストでは 10 μm 程度しか堪えられないことが分かっているため、その他にレジスト用のワックスを用いてエッチングを試みた。このワックスは現在用いているエッチャントに対し、十分な耐性があり 100 μm 以上のエッチングが可能である。しかし、粘性がとても強いため形状の形成は難しい。このため今回このワックスを使用することは断念した。Au をマスクとして使用可能であるか確かめた。

Si 基板に Au を蒸着・アロイした後、 $HF + HNO_3 + CH_3COOH$  でエッチングを行った。30min、60min、90min の条件で行った結果、Au はどの基板にも残っており、段差計で測定不可能な程の深いエッチングができた。膜圧計で測定を試みると、 $100~\mu m$  以上のエッチングが行われていた。この結果から Au はマスクとして使用可能であることが確かめられた。

上記の工程を行いメサ構造の作製に成功した。その結果を示す。

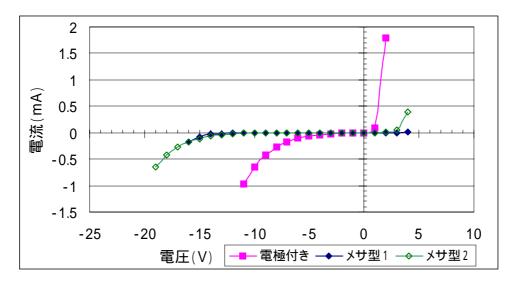

図 31 メサ型構造 I-V 特性

メサ型1、メサ型2は同じ試料であるが、図30のようにメサ型に分割されているため、電極箇所により特性が変化している。

図 31 から、メサ型構造とすることでリーク電流・暗電流を減らし、逆方向特性が改善されることが分かった。順方向に関してはエッチャントに Al 側電極が削られたのではないかと考えられる。残念ながら光電流の確認は出来なかった。

# 6.2 処理工程の提案

メサ構造にしたもので光電流が得られなかった原因として次の 4 要因が挙げられる。

不純物濃度が高すぎて空乏層が Ge 層まで達していない 発生したキャリヤがヘテロ障壁を乗り越えられない Ge の 1.55 µm に対する吸収係数が低いため発生キャリヤが少ない 光源の出力が小さすぎる。

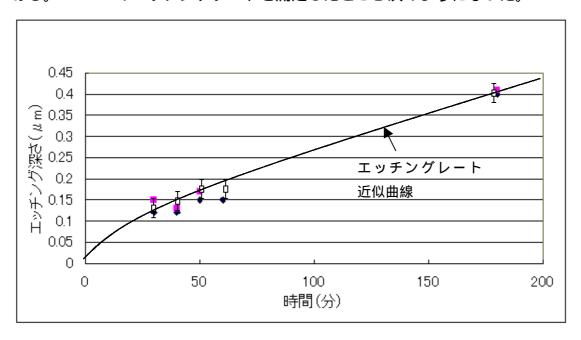

~ のいずれの理由が原因にしても、第3章で述べたように、そのため p-Si 層を薄くすることが必要である。 p-Si 層は現在1  $\mu$ m であるので手動による研磨で薄くするのはまず不可能である。よってエッチングを行うことにする。現在調べている中で、Si に対しもっとも遅いエッチングレートの薬品は B-HF である。 B-HF のエッチングレートを測定したところ次のようになった。

図 32 B-HF のエッチングレート (22 )

エッチングレートは本研究室の環境で再現可能な 22 で行った。 図 32 のように約 3 時間(180min)で 0.41 μm であるからおおよそ 2.28 n m/min

である。

3 章で述べたように必要だけ空乏層を伸ばすためには 500~750nm 削れば良

いことがわかる。そのため  $219 \sim 329 \min$  のエッチングが必要であるといえる。これを行うと Ge まで空乏層を広げるのに必要な電圧は  $10 \sim 20 V$  程度で可能であることが計算から分かる。障壁を乗り越えさせる目的もあるので、出来るだけ高いバイアス電圧で動作させるの良い。このことから、  $22 \quad \text{で } 4 \sim 6$  時間の B-HF 処理を行えば成功する可能性があることが分かる。

# 6.3 光起電力の測定

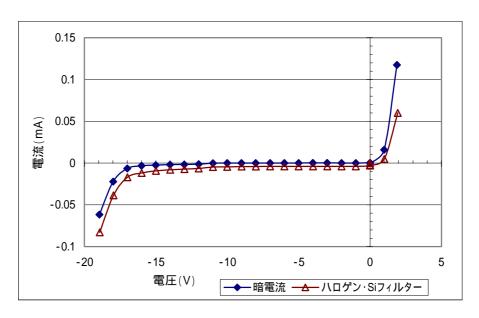

次に、光源の出力を変えることで光起電力効果の測定を試みた。ここで、光源としてハロゲンランプを用いた。そのままの光では Si の吸収波長も試料に照射してしまうため、フィルタとして Si のウェハを通した光を照射した。

図 33 光起電力効果

図 33 から Ge 層で光吸収しているという確証はないが、光に何らかの反応を見せている事がわかる。

# 6.4 本章のまとめ

# 本章では、

メサ構造の作製を実現するため Si の深いエッチング方法について検討した。 その結果 Au をマスクとする方法を採り、100 μm 以上のエッチングを行った。

- ・ メサ型構造の作製工程を提案し、その実現に至った。

- ・ APD としての実現にむけて、検討を行い、処理工程の提案を述べた。

- ・ 光源を変えることで光源の波長範囲、出力パワーを上げ光電流の確認をすることが出来た。

# 第7章 結言

本研究では、光通信用の受光素子として、Ge/Si-APD の有効性を明らかにし、その実現を目指してウェハボンディング手法により Si/Ge ヘテロ接合を形成した。ウェハボンディング工程の詳細を検討することにより 90%程度の歩留りで、ヘテロ接合形成に成功した。本研究で得た結論と今後の課題についてまとめる。

- 1) 理論検討からなだれ増倍層となる p-Si 層に必要な条件、すなわち不純物 濃度と厚みの関係を明らかにした。これに基づき、 n <sup>+</sup>-Si 上に p-Si をエ ピタキシャル成長した結晶を入手した。

- 2) ウェハボンディング手法の確立を目指し、p-Ge/p-Ge、p-Ge/n-Si、p-Ge/p-Si、のそれぞれの組み合わせで最適なボンディング条件を明らかにし、これらの結果に基づき、目的とする pn-Si/p-Ge のボンディング成功に至った。

- 3) ボンディングの成功率を高めるため各ウェハの処理温度と処理時間について条件の最適化を行い、pn-Si/p-Geにおいて90%程度の歩留りで接合形成に成功する条件を見出した。

- 4) さらに APD 構造として必要なメサ型構造作製に向けて Si の深いエッチング工程を検討した。素子の各工程毎の I-V 特性を明らかにし、最終目標となるメサ型構造の作製に成功した。

なお、現在までの所、用いたウェハの p-Si 不純物濃度が設計値よりも高く、Ge で発生したキャリヤがヘテロ界面を乗り越えて p-Si に注入されないため、1.55 μm 帯の光に対する応答が明確に見られていない。しかし、本研究により、1.55 μm 帯の光に高い受光感度を持ち、かつなだれ増倍過程で発する過剰雑音を低減した APD の実現が可能であるという見通しを得た。

今後、設計通り空乏層がヘテロ界面に達しえるようにするため、B - HF 処理などによりエッチングし、p-Si 層の厚さを制御する予定である。これにより波長 1.55 μm の光に対する応答が得られるものと期待できる。

# 謝辞

本研究を進めるにあたりご指導、ご鞭撻頂きました高知工科大学 電子・光 システム 神戸宏教授に深く感謝します。

日頃研究を進めるにあたり試料作製、実験の補助に惜しみなく協力してくれ た坂元誠氏に深く感謝します。

ウェハボンディングに関し基礎データを残し、多くの参考資料の提供をして くださった加瀬川亮氏、大橋律男氏に感謝します。

日頃からともに研究に励み、意見を交しあい協力いただいた前田康彦氏、木本薫宏氏、川内悠輔氏、山田和弘氏に感謝します。

カーブトレーサー装置を貸して頂き、多くの助言を頂いた河津哲教授に感謝いたします。副担当教員であり、鉄シリサイド試料の提供をしていただいた高知工科大学物質・環境システム 谷脇雅文教授に感謝いたします。

副審査員であり、助言を頂いた成沢忠教授、八田章光助教授に感謝いたします。

6年間お世話になりました高知工科大学電子・光システムコース原央コース長はじめ教職員の皆様に感謝いたします。

# 参考文献

- [1] 例えば、末松安晴,伊賀健一,"光ファイバ通信入門"(改訂3版),オーム社,1989,p145 and 202

- [2] S.M.Sze and G. Gibbons, "Avalanche breakdown voltage of abrupt and linearly graded p-n junctions in Ge,Si,GaAs and GaP,"Appl. Phys. Lett.,8,111(1966)

- [3] C.A. Armiento, S.H. Groves, and C.E.Hurwiz, "Ionization coefficients of electrons and holes in InP," Appl. Phys. Lett., 35, 333(1979).

- [4] R.J. McIntyre,"Multiplication noise in uniform avalanche diodes," IEEE Trans. Electron Devices, ED-13, 164(1966).

- [5] R.J. McIntyre, "The distribution of gains in uniformaly multiplying avalanche photodiodes: theory," IEEE Trans. Ellectron Devices, ED-19, 703(1972).

- [6] J.Conradi,"The distribution of gains in uniformly multiplying avalanche phtodiodes: experimental,"IEEE Trans. Electron Devices, ED-19,713(1972).

- [7]P.P.Webb, R.J.McIntyre, and J.Conradi, "Properties of avalanche photodiodes," RCA Rev., 35, 234(1979)

- [8]神戸宏, "レーザー学会第 294 回研究会報告", pp. 15-19, 2001

- [9]A.R.Hawkins, W.Wu, P.Abraham, K.Streubel, and J.E.Bowers, Appl. Phys. Lett., 70,303.1997

- [10] W.Wu, AR. Hawkins, and J.E. Bowers, SPIE, 3006, 38, 1997

- [11] 米津宏雄, "光通信素子工学", 工学図書株式会社, 1984

- [12] J.L.Moll, "Physics of Semiconductors," McGraw-Hill, Inc., New York(1964)

- [13]S.L.Miller, "Avalanche breakdown in germanium, "Phys.Rev.,Vol.99,No.4, pp.1234-1241 ,1955

- [14] 大西健一,坂元誠,神戸宏 , "電気関係四国支部連合大会", p194,2002

- [15] H.Melchior, "Laser Handbook," Vol. 1, North Holland Publishing Company, 1972

- [16] F.Capasso, M.B. Panish, S. Sumski, and P.W. Foy, Appl. Phys. Lett., 36, 165, 1980

- [17] W.M.Becker, A.K.Ramdas, and H.Y.Fan, J.Appl. Phys., Suppl. to 32, 2094, 1961

- [18] S.M.Sze and J.C.Irvin,"Resistrity, Mobility, and Inpurity Levels in GaAs, Ge, and Si at 300k, "Solid State Electron, 11, 599, (1968).

- [19] J.C.Irvin,"Resistivity of Bulk Silicon and Diffused Layers in Silicon,"Bell systvTech.J.,41,387(1962)

- [20]W.F.Beadle,R.D.Plummer,andJ.C.C.Tsai,QuickReference Manual for Semiconductor Engineers

- [21] S.M. Sze,"Physics of semiconductor Devices,"Wiley-Interscience, New York(1969)

- [22] S.M.Sze,"Physics of semiconductor Devices second edition p76,1981.

- [23] Andrew S.Geove,"Physics and Technoloogy of Semiconductor Device " オーム社、 p 110 , 1995