# DEVELOPMENT DESIGN OF BUILT-IN SELF-TEST FOR LSI CIRCUITS: TEST PATTERN GENERATION, OSCILLATION-BASED TESTING, AND CALIBRATION TECHNIQUE

| 著者     | WANNABOON Chatchai               |

|--------|----------------------------------|

| year   | 2018-09                          |

| 学位授与機関 | 高知工科大学                           |

| 学位授与番号 | 26402甲第341号                      |

| URL    | http://hdl.handle.net/10173/1989 |

# DEVELOPMENT DESIGN OF BUILT-IN SELF-TEST FOR LSI CIRCUITS: TEST PATTERN GENERATION, OSCILLATION-BASED TESTING, AND CALIBRATION TECHNIQUE

A dissertation submitted to Kochi University of Technology in partial fulfillment of the requirements for the degree of Doctor of Philosophy

1198007 Chatchai Wannaboon

Advisor Prof. Masayoshi Tachibana

Electronic and Photonic Systems Engineering Course Graduate School of Engineering, Kochi University of Technology

August 2018

The title of this dissertation on September 5, 2018 was "DEVELOPMENT DESIGN OF BUILT-IN SELF-TEST FOR LSI CIRCUITS: TEST PATTERN GENERATOR, OSCILLATIONBASED TESTING, AND CALIBRATION TECHNIQUE," and it was modified on September 20, 2018.

#### Abstract

There are three major activities in the life-cycle of an ICs product, i.e. design, manufacturing, and testing. A robust design and proper manufacturing environment provide a quality performance of the devices. Besides, testing is required to improve a reliability of the manufactured ICs. Despite outstanding design and fabrication process, it is futile to achieve a complete quality ICs without a suitable testing strategy. Typically, testing is required in every phases in the life-cycle of the ICs product. In other words, testing, in terms of design verification, identifies numerical errors during the design phase. Likewise, during the fabrication process, testing prevents any manufactured defects and ensure the quality of the designed product. Testing also seeks to detect functional faults that sustained during operation.

Rising of the transistor technology has evolved the electronic industry substantially. From the visible with normal size, nowadays, modern electronics device is implemented and operated on a Nano-scale and tends to reducing every year. Meanwhile, the size of electronics device is decreasing, the quality is approaching to the opposite direction. In other words, the quantity and diversity of transistors is increasing, and become a high complex network. This situation has led to a great demand of reliable System on Chip (SoC). Testing such devices before a manufacturing process has become a crucial issue. Although, an off-chip testing with automated test equipment has been used commercially, it requires costly measurements with long-time process. For contemporary Large Scale Integrated (LSI) circuits, automated on-chip testing has gained a great attention on either research or industrial area. Built-in Self-Test (BIST) and Design-for-Test (DFT) are the major strategies, which have been widely accepted by meaning of improving observability and controllability during the testing process.

This dissertation presents effective designs of BIST systems for a defect-oriented testing in analog and mixed-signals LSI circuits. Fully on-chip circuitry, high faults detection against catastrophic and parametric variation, and low performance degradation are the objectives of this work. The proposed methods focus on the principal of BIST, i.e. test stimulus generation, test control, and test response analysis. Such methods are implemented for essential LSI building blocks, ranging from transistor-only circuitry such as an operational amplifier (Op Amp) and comparator, to an analog low-pass filter, as well as a large-scale mixed-signals system. The major contributions of this dissertation can be classified into three approaches. The first approach is designing a high-speed random signals generator for the source of test stimulus generation. The second approach is the demonstration of an oscillation-based testing in order to eliminate the large stimulus generator. The third approach involves the combination of self-test and calibration technique for each circuit elements.

The proposed methods of this dissertation begins with a high-data-rate true random bit generator for a cost-effective and high-speed test stimulus generation. This method is a full-custom design of chaos-based True Random-Bit Generator (TRBG) implemented on a 0.18- $\mu m$  CMOS technology with unique composition of three major components, i.e. (i) chaotic jerk oscillator, (ii)  $\Delta\Sigma$  modulator, and (iii) simple pre/post-processing. A chaotic jerk oscillator is a deterministic source of randomness that potentially offers robust and highly random chaotic signals and exhibits a distinctive property of smoothly balanced-to-unbalanced alternation of double-scroll attractors. The continuous-time  $2^{nd}$ -order  $\Delta\Sigma$  modulator is introduced as a mixed-signal interface in order to increase a resolution of random bit sequences while no extra clock is required. The  $\Delta\Sigma$  modulator is constructed mainly by a folded-cascode amplifier with sufficient gain and phase margin of 64dB and 83°, respectively, and a high-speed comparator with a time constant of 2.7ns. An uncomplicated structure of shift-registers is realized as a post-processing

process. The bit sequence of the proposed TRBG successfully passes all statistical tests of NIST SP800-22 test suite, and the ultimate output bit rate is 50Mbps. The physical layout of a chip area is 212.8  $\times$  177.11  $\mu m^2$  and the DC power dissipation is 1.32mW using a 1.8-V single supply voltage.

The second method, a simple design-for-testability (DFT) technique for analog second-order  $\Delta\Sigma$  modulators is described. The structure of circuit-under-test is modified and operated as two symmetric structure circuits in the test mode. Different DC offset and simple digital counters are connected to the input and output of the circuit in order to reduce testing process complications and costs, with the modulator operated as a simple signal generator in the test mode. A demonstration of the testing process is performed through the switched-capacitor second-order  $\Delta\Sigma$  modulator, which achieves several advantages, including low cost, high-speed testing, and high fault coverage, and covers parametric failure. Also, the overall system was fully fabricated in 0.18- $\mu$ m CMOS standard technology without the need for additional digital processing units.

Additionally, a phase difference analysis technique is presented in the third method, which is sensitive to the parametric deviations and allows a tolerance band of passive analog components. Test operations can be simply achieved by comparing the phase difference between a reference clock signal and a reconfigured circuit-under-test (CUT) as an oscillator. The difference of phase characteristics between the two signals can be utilized as an indicator for a fault signature, which can be characterized by a compact digital circuit comprising a counter and logic components. Simulation of faults detection reveals a high faults coverage, high-speed testing, and tolerance band controllability. The proposed technique has offered a fully on-chip BIST in 0.18- $\mu m$  CMOS standard technology with no external test equipment required.

Furthermore, the integration of BIST and calibration technique is proposed in the forth method. simple circuitry such as a frequency-to-DC circuit, a windows compara-

tor, and basic logic elements are utilized as the faults detection circuits. The calibration system is additionally implemented through the resistor array with a feedback network in order to adjust the gain value of the CUT. Simulation results show the capable of faults detection involves catastrophic and parametric variation. Moreover, the signals-to-noise ratio (SNR) of the CUT can be preserved at the acceptable level against the failure circuitry.

key words Built-In Self-Test, Test and Calibration Technique, Oscillation-Based Testing, True Random Bit Generation, Chaotic Oscillator, Design-for-Structural-Testability.

# Contents

| Chapte | er 1 I | Introduction                                                            | 1  |

|--------|--------|-------------------------------------------------------------------------|----|

| 1.1    | An ov  | rerview of Mixed-Signal Testing                                         | 3  |

| 1.2    | Defect | ts in the Integrated Circuits                                           | 4  |

| 1.3    | Brief  | Classification of Testing Architecture                                  | 6  |

| 1.4    | Objec  | tives of this Dissertation                                              | 8  |

| 1.5    | Disser | rtation Organization                                                    | 8  |

| Chapte | er 2   | Frue Random Bit Generator for High-Speed Testing in $\Delta\Sigma$      |    |

| Modul  | ator   |                                                                         | 11 |

| 2.1    | Review | w on the conventional True Random Bit Generator                         | 12 |

| 2.2    | An Au  | utonomous Chaotic Jerk Model                                            | 15 |

|        | 2.2.1  | All-CMOS Chaotic Jerk Oscillator                                        | 15 |

|        | 2.2.2  | Chaotic Dynamics Evaluation                                             | 20 |

| 2.3    | Propo  | sed Architecture of a TRBG through $\Delta\Sigma$ Modulation of Chaotic |    |

|        | Jerk S | Signals                                                                 | 23 |

|        | 2.3.1  | Signals Scrambling Circuit                                              | 26 |

|        | 2.3.2  | The Continuous-Time $\Delta\Sigma$ modulator                            | 27 |

|        | 2.3.3  | Post-Processing Unit                                                    | 29 |

| 2.4    | True I | Random Bits Generator Evaluation                                        | 30 |

|        | 2.4.1  | Cross-Correlation, Autocorrelation and Entropy                          | 31 |

|        | 2.4.2  | NIST SP800-22 Standard Test Suite                                       | 34 |

|        | 2.4.3  | TestU01 Empirical Test Suite                                            | 35 |

|        | 2.4.4  | Performances Measurement Results                                        | 38 |

| 2.5    | Rist T | Pechnique based on Chaotic Stimulus                                     | 38 |

#### Contents

|                               | 2.5.1  | Experimental Results                                            | 41         |

|-------------------------------|--------|-----------------------------------------------------------------|------------|

| 2.6                           | Conclu | usion                                                           | 43         |

| 2.7                           | Refere | ence                                                            | 44         |

| Chapte                        | er 3 A | A Design-for-Structural-Testability for Simple Faults De-       |            |

| tection                       | in An  | nalog $\Delta\Sigma$ Modulator                                  | 49         |

| 3.1                           | Review | w on Design-for-Testability in the $\Delta\Sigma$ Modulator     | 50         |

| 3.2                           | Design | n-For-Structural-Testability (DFST)                             | 51         |

| 3.3                           | Propo  | sed DFST For Analog $\Delta\Sigma$ Modulator                    | 55         |

|                               | 3.3.1  | DFST for the Second-order $\Delta\Sigma$ Modulator Architecture | 55         |

|                               | 3.3.2  | Faults Detection                                                | 56         |

| 3.4                           | Overa  | ll Circuits Design                                              | 58         |

|                               | 3.4.1  | Operational Amplifier                                           | 58         |

|                               | 3.4.2  | Dynamic Comparator                                              | 58         |

|                               | 3.4.3  | Modulator Performance                                           | 60         |

| 3.5                           | Simula | ation Results                                                   | 61         |

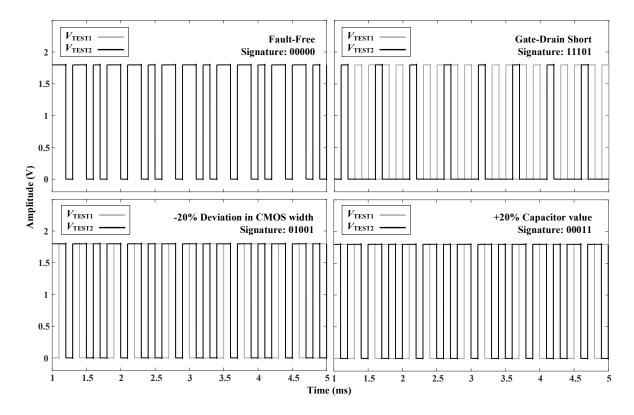

|                               | 3.5.1  | Faults Models                                                   | 62         |

|                               | 3.5.2  | Testing Results                                                 | 67         |

| 3.6                           | Conclu | usion                                                           | 68         |

| 3.7                           | Refere | ence                                                            | 69         |

| $\mathbf{Chapt}_{\mathbf{c}}$ | er 4 H | Phase Difference Analysis Technique for Parametric Faults       |            |

| BIST i                        | in CM  | OS Analog Circuits                                              | <b>7</b> 3 |

| 4.1                           | Review | w on Parametric Faults Detection in Analog Circuits             | 73         |

| 4.2                           | Phase  | Difference Analysis Technique                                   | 75         |

|                               | 4.2.1  | The Proposed Technique for the BIST                             | 77         |

|                               | 400    | Faulta Dataction                                                |            |

#### Contents

| 4.3    | The System Architecture                                                        |                                                                                                |     |

|--------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|

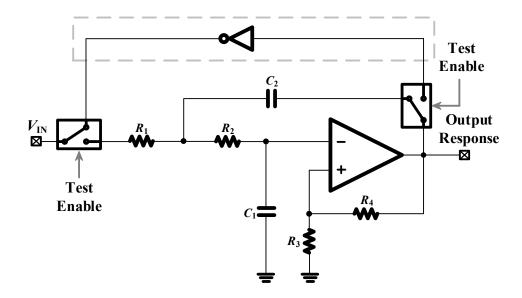

|        | 4.3.1                                                                          | A Modified Sallen-Key Low Pass Filter as the Oscillator                                        | 78  |

|        | 4.3.2                                                                          | An Operational Amplifier                                                                       | 79  |

| 4.4    | Simula                                                                         | ation Results                                                                                  | 80  |

| 4.5    | Concl                                                                          | usion                                                                                          | 83  |

| 4.6    | Refere                                                                         | ence                                                                                           | 84  |

| Chapte | er 5 I                                                                         | BIST and Calibration Technique in Continuous-Time $\Delta\Sigma$                               |     |

| Modul  | ator                                                                           |                                                                                                | 86  |

| 5.1    | Review                                                                         | ws on $\Delta\Sigma$ Modulator with BIST and Calibration Technique                             | 86  |

| 5.2    | Proposed BIST with Self-Calibration System for Analog $\Delta\Sigma$ Modulator |                                                                                                | 90  |

| 5.3    | Overa                                                                          | ll Circuits Description and Operation                                                          | 91  |

|        | 5.3.1                                                                          | Frequency-to-DC Converter                                                                      | 91  |

|        | 5.3.2                                                                          | Windows Comparator and Control Calibration Circuit                                             | 92  |

|        | 5.3.3                                                                          | Continuous-Time Fully Differential $2^{nd}\text{-}\mathrm{order}\ \Delta\Sigma$ Modulator with |     |

|        |                                                                                | Gain Compensation                                                                              | 93  |

| 5.4    | Simula                                                                         | ation Results                                                                                  | 95  |

| 5.5    | 6 Conclusion                                                                   |                                                                                                | 99  |

| 5.6    | Refere                                                                         | ence                                                                                           | 100 |

| Chapte | er 6 (                                                                         | Conclusion                                                                                     | 103 |

| Ackno  | wledge                                                                         | ment.                                                                                          | 107 |

# List of Figures

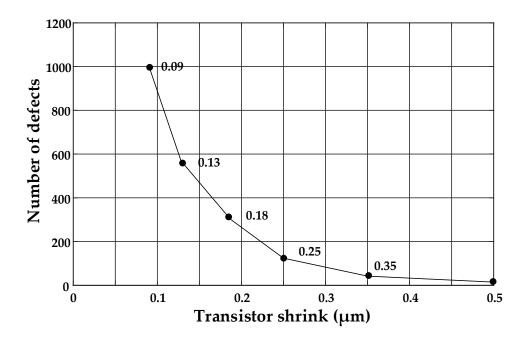

| 1.1  | Number of defects versus transistor shrinking size                                                                      | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

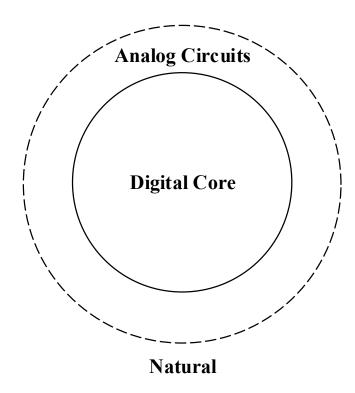

| 1.2  | The role of analog circuits in overall electronically process                                                           | 3  |

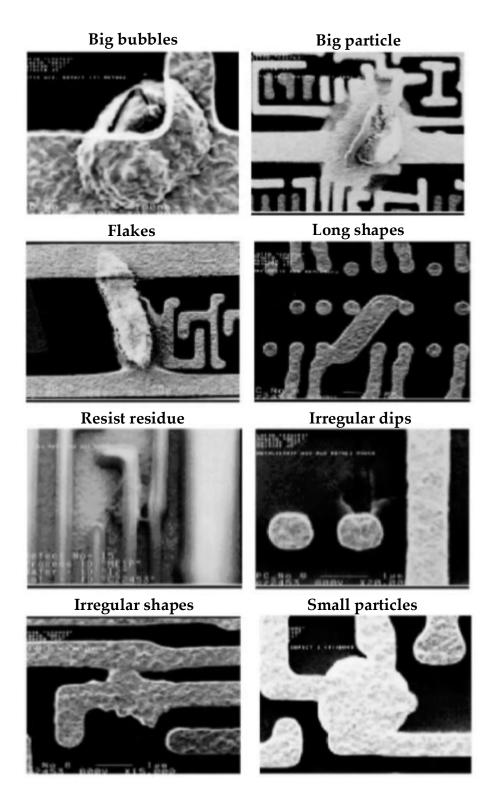

| 1.3  | Sample of defects in manufactured ICs                                                                                   | 5  |

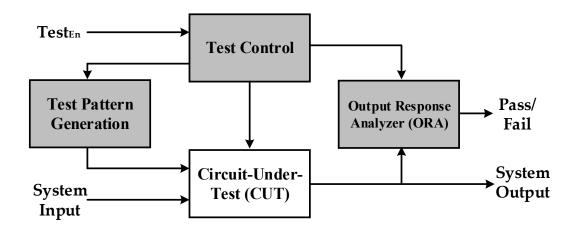

| 1.4  | Basic BIST architecture                                                                                                 | 6  |

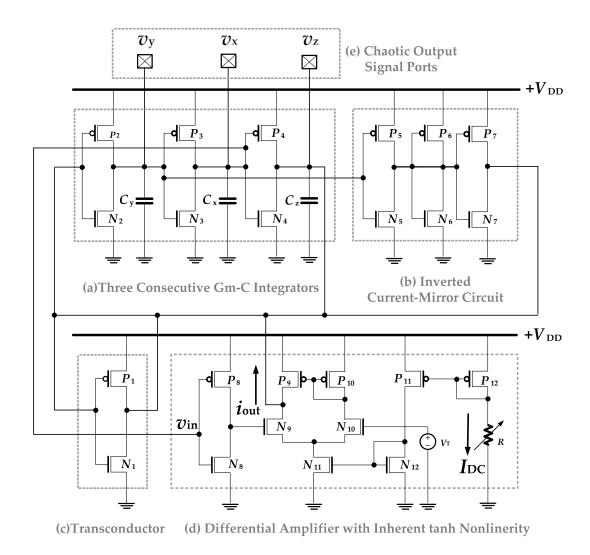

| 2.1  | The proposed circuit configuration of chaotic jerk oscillator                                                           | 14 |

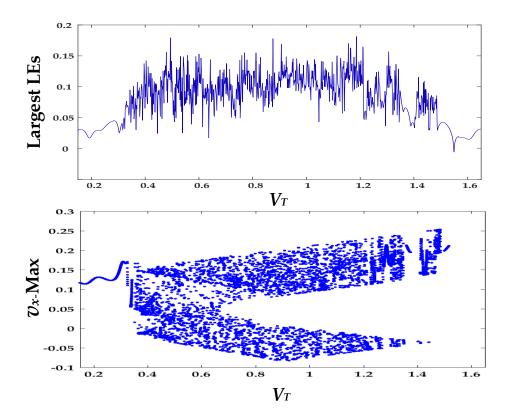

| 2.2  | Plots of the spectrum of LLEs and Bifurcation diagram of $\mathbf{X}_{max}$ over a                                      |    |

|      | tuning voltage $V_T$                                                                                                    | 17 |

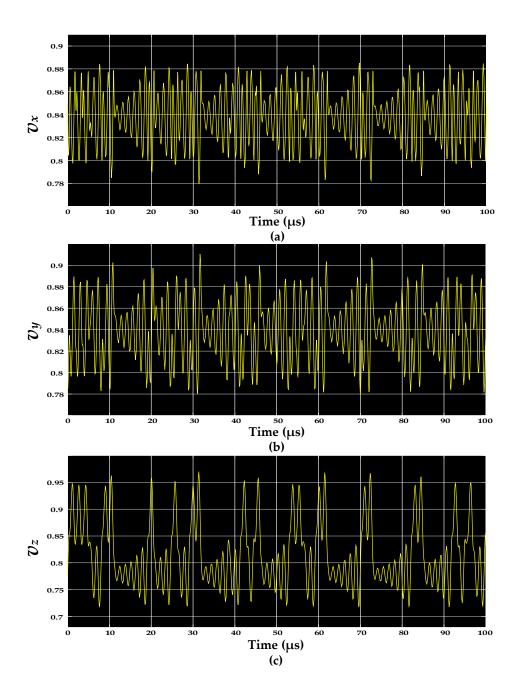

| 2.3  | Chaotic waveform in time-domain of (a) $\mathbf{v}_x$ , (b) $\mathbf{v}_y$ , and (c) $\mathbf{v}_z$ at $\mathbf{V}_T =$ |    |

|      | 0.9V                                                                                                                    | 18 |

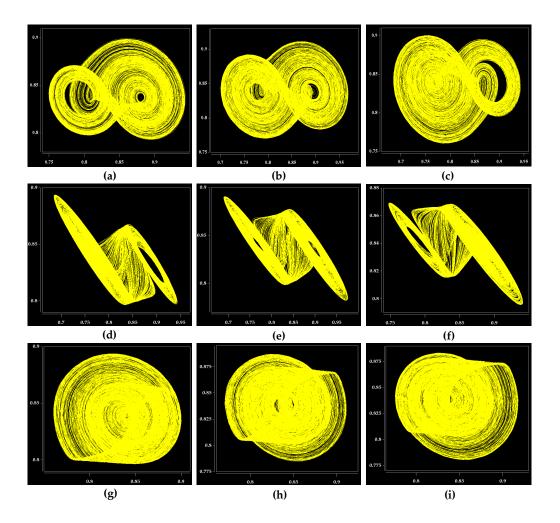

| 2.4  | Two-dimensional strange attractor with different tuning the voltage $\mathbf{V}_T$                                      |    |

|      | obtained from the proposed oscillator, between (a-c) $\mathbf{v}_x$ - $\mathbf{v}_y$ , (d-f) $\mathbf{v}_x$ -           |    |

|      | $\mathbf{v}_z$ , (g-i) $\mathbf{v}_y$ - $\mathbf{v}_z$                                                                  | 19 |

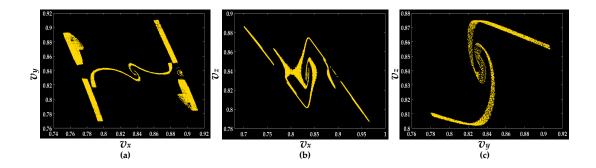

| 2.5  | Poincarè mapping in planes where (a) $v_z = 0.84$ , (b) $v_y = 0.84$ , and (c)                                          |    |

|      | $v_x = 0.84. \dots$                                                                                                     | 20 |

| 2.6  | Block diagram of the proposed TRBG with $\Delta\Sigma$ modulation of chaotic                                            |    |

|      | jerk signals                                                                                                            | 21 |

| 2.7  | Histograms of the chaotic jerk signals at (a) $v_x$ , (b) $v_x$ , (c) $v_x$ , and (d)                                   |    |

|      | after scrambling process                                                                                                | 21 |

| 2.8  | Block diagram and a circuit of the signals scrambling technique                                                         | 22 |

| 2.9  | The single-bit second-order $\Delta\Sigma$ modulator with feed-forward topology                                         | 23 |

| 2.10 | (a) Folded-cascode operational transconductance amplifier and (b) a dy-                                                 |    |

|      | namic comparator                                                                                                        | 24 |

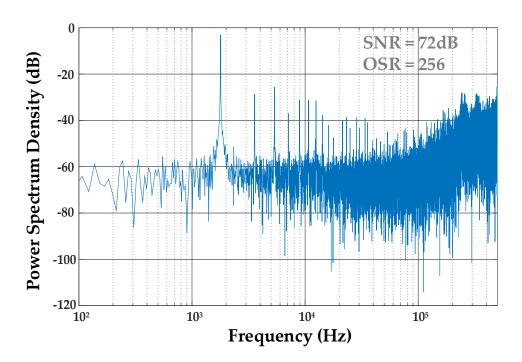

| 2.11 | Output power spectrum density of the modulator                                                                          | 25 |

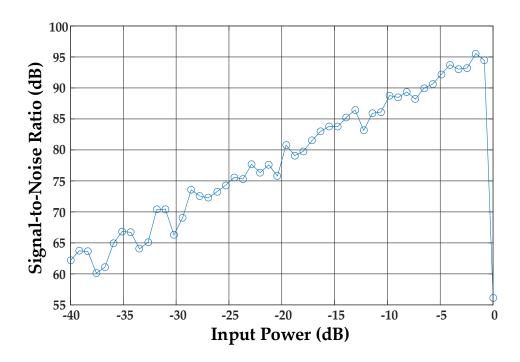

| 2.12 | Signal-to-noise ratio as a function of normalized input power                  | 25 |

|------|--------------------------------------------------------------------------------|----|

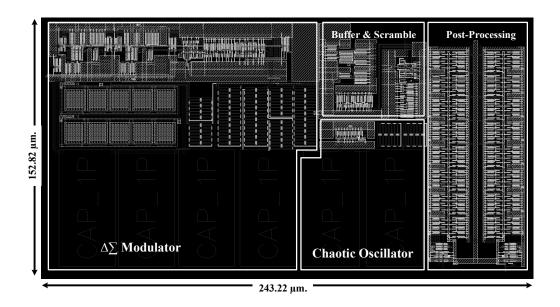

| 2.13 | Layout diagram of overall circuits in 0.18- $\mu$ m CMOS standard technology.  | 26 |

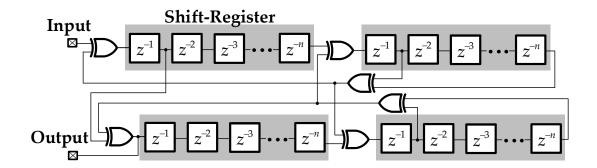

| 2.14 | Post-processing unit structure                                                 | 29 |

| 2.15 | Correlation analysis between the output binary sequences, (a) normalized       |    |

|      | cross-correlation, and (b) autocorrelation                                     | 31 |

| 2.16 | The entropy of difference 1,000 sets of the output binary sequences            | 32 |

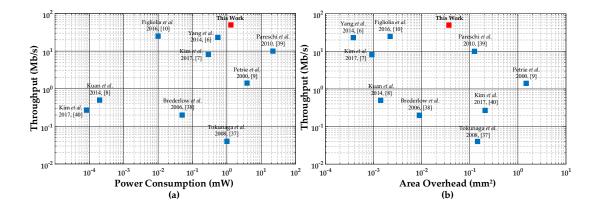

| 2.17 | Comparison of normalized throughput versus (a) power consumption and           |    |

|      | (b) total area with previous works                                             | 38 |

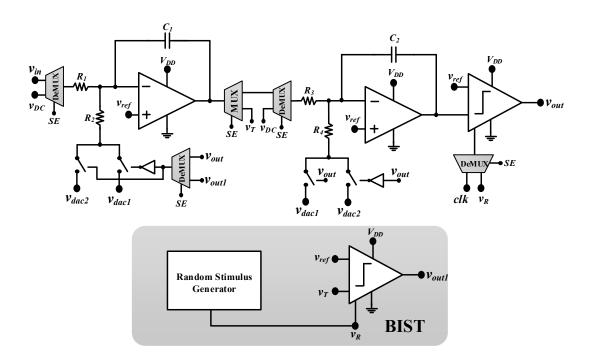

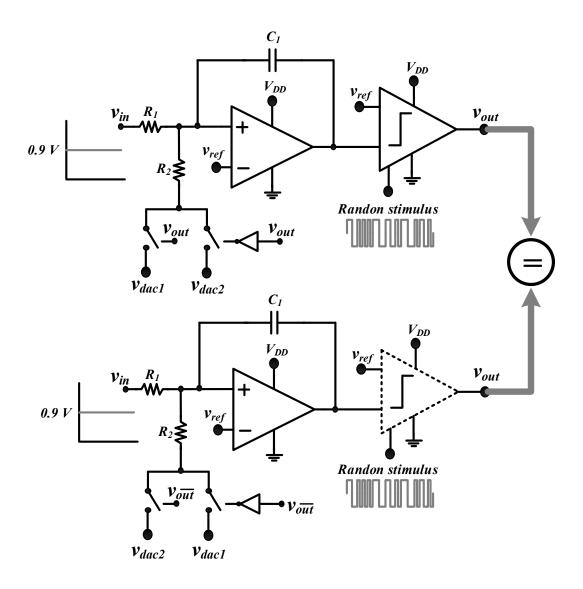

| 2.18 | Circuit diagram of the proposed BIST system                                    | 39 |

| 2.19 | The separated CUT in the test mode                                             | 40 |

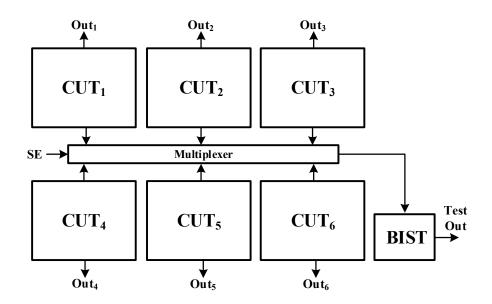

| 2.20 | Overall BIST system with multi-CUTs                                            | 41 |

| 2.21 | Comparison between two outputs testing response from (a) CUT1, (b)             |    |

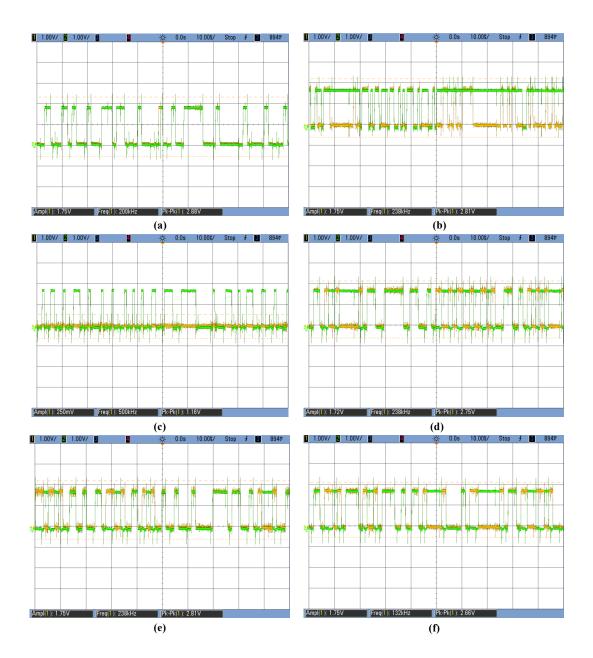

|      | CUT2, (c) CUT3, (d) CUT4, (e) CUT5 and (f) CUT6                                | 42 |

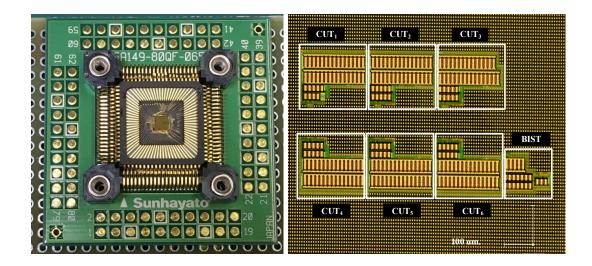

| 2.22 | Chip micro-photograph of the overall system with area of 0.294 $\mathrm{mm}^2$ | 43 |

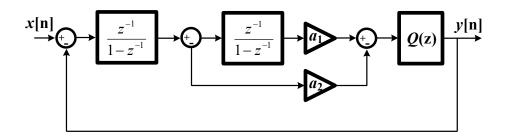

| 3.1  | Block diagram of the single-loop second-order $\Delta\Sigma$ modulator         | 53 |

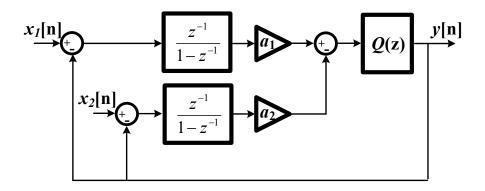

| 3.2  | Reconfigured model in the test condition                                       | 53 |

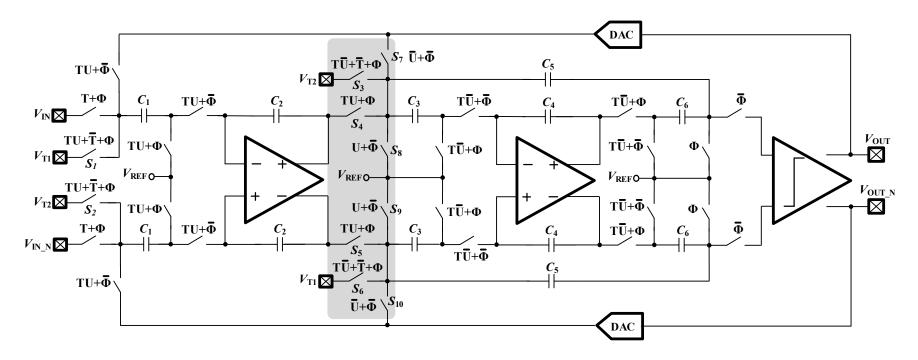

| 3.3  | Overall schematic of the proposed DFST $\Delta\Sigma$ modulator                | 54 |

| 3.4  | The reconfigured modulator in test mode when the control signal $U$ is         |    |

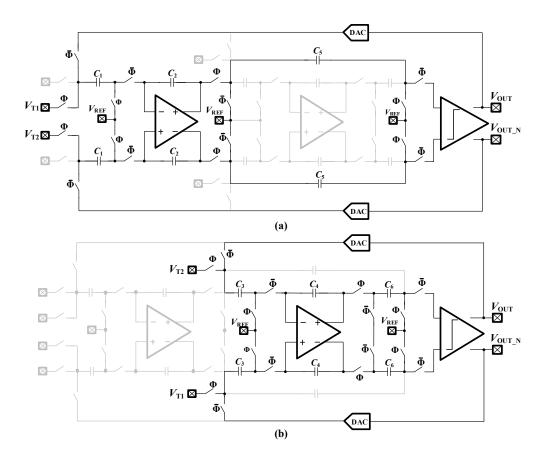

|      | set to 0 (a), and 1 (b)                                                        | 55 |

| 3.5  | The reconfigured modulator in test mode when the control signal $U$ is         |    |

|      | set to 0 (a), and 1 (b)                                                        | 57 |

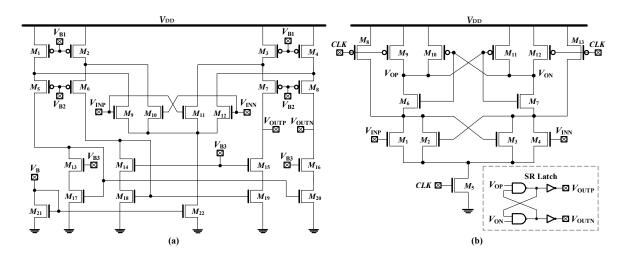

| 3.6  | Class B, fully-differential folded-cascode operational amplifier (a), and      |    |

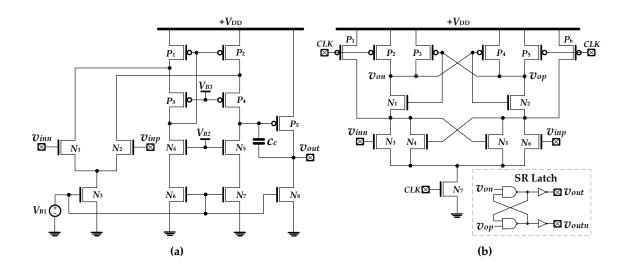

|      | cross-coupled dynamic comparator with SR latch (b)                             | 60 |

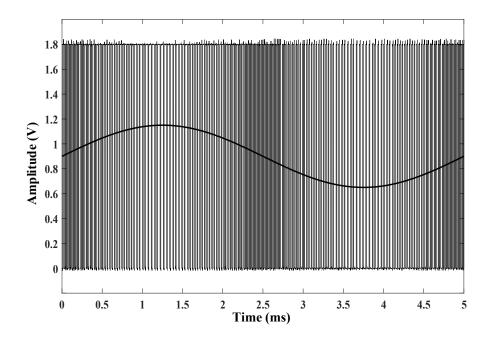

| 3.7  | Transient waveform of an input sinewave and modulated output                   | 61 |

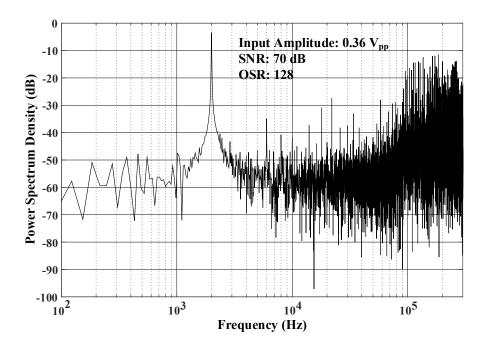

| 3.8  | Output power spectrum density of the proposed modulator                        | 62 |

| 3.9  | Testing output response of four demonstrating CUTs                                    | 63 |

|------|---------------------------------------------------------------------------------------|----|

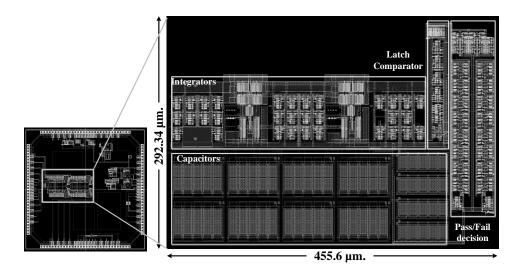

| 3.10 | Layout diagram of the proposed DFST $\Delta\Sigma$ modulator                          | 68 |

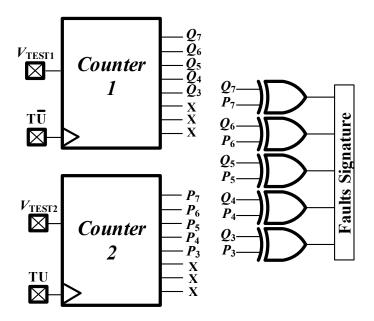

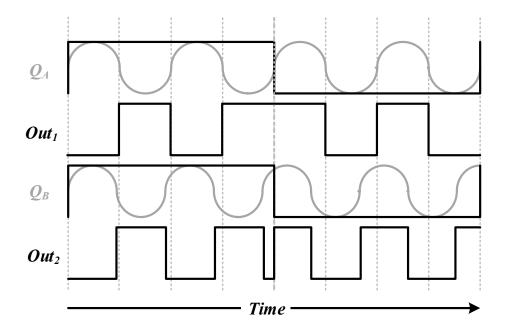

| 4.1  | Generation of faults signature using phase difference technique                       | 74 |

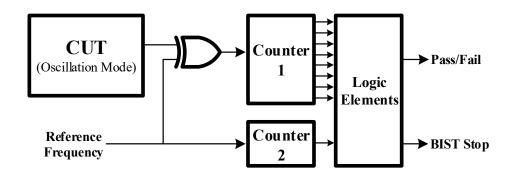

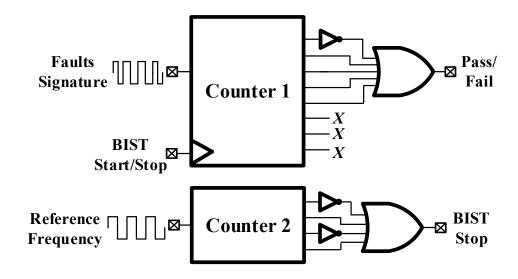

| 4.2  | Block diagram of the proposed system                                                  | 76 |

| 4.3  | Demonstration of the pass/fail decision circuit                                       | 76 |

| 4.4  | Reconfigured model in the test condition                                              | 78 |

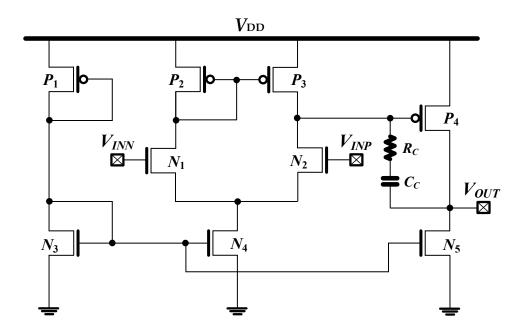

| 4.5  | The two-stage operational amplifier with RC compensation                              | 79 |

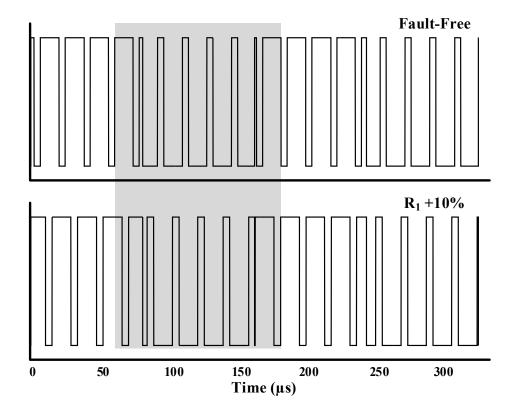

| 4.6  | The output waveform in transient between the fault-free and faulty cir-               |    |

|      | cuit                                                                                  | 81 |

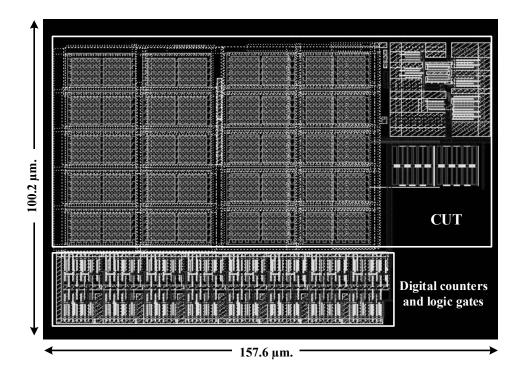

| 4.7  | The layout diagram of overall circuits in 0.18- $\mu m$ CMOS technology               | 83 |

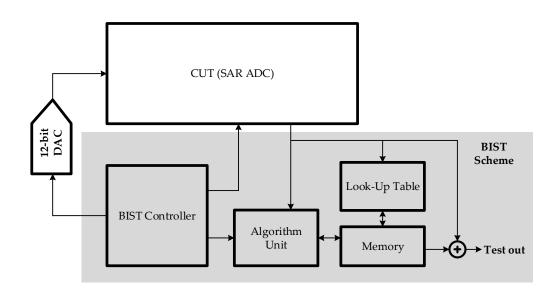

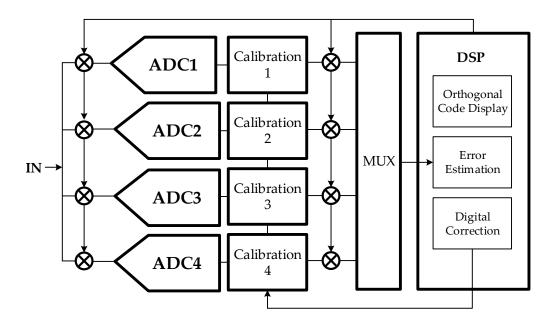

| 5.1  | Block diagram of BIST based on stimulus error identification algorithm                |    |

|      | in ADC (jin et al.)                                                                   | 87 |

| 5.2  | Built-in Self-Calibration (BISC) scheme for Time-Interval ADC (Mariano                |    |

|      | et al.)                                                                               | 88 |

| 5.3  | Built-in Self-Calibration (BISC) scheme for Time-Interval ADC (Mariano                |    |

|      | et al.)                                                                               | 89 |

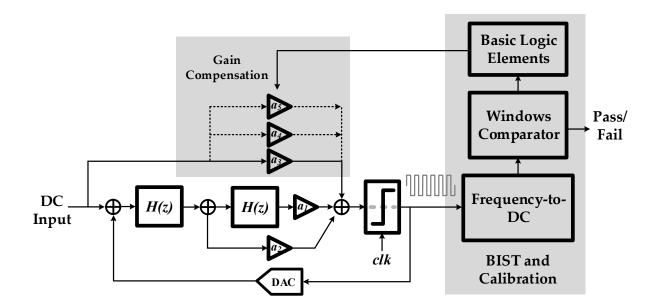

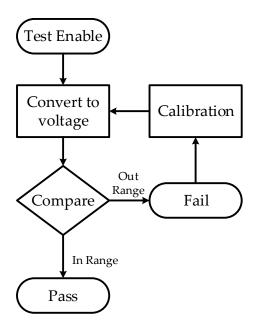

| 5.4  | Block diagram of the proposed BIST with self-calibration system                       | 90 |

| 5.5  | Flowchart of the system operation                                                     | 91 |

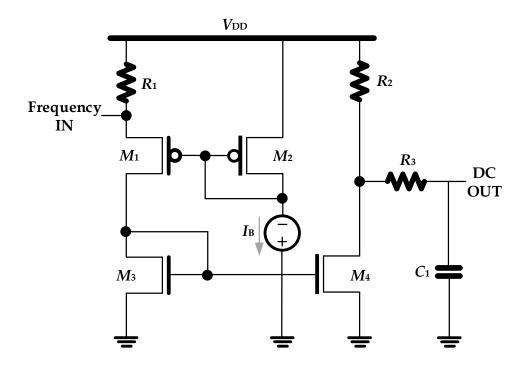

| 5.6  | The frequency-to-DC converter                                                         | 92 |

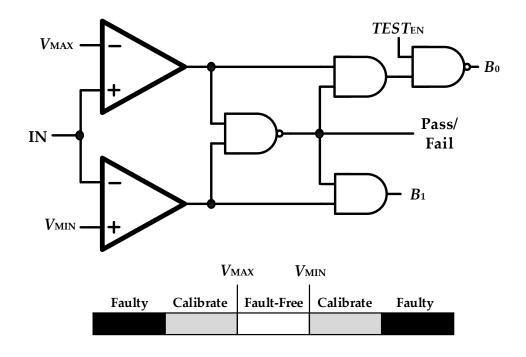

| 5.7  | The windows comparator and acceptation regions of the analog circuit                  | 93 |

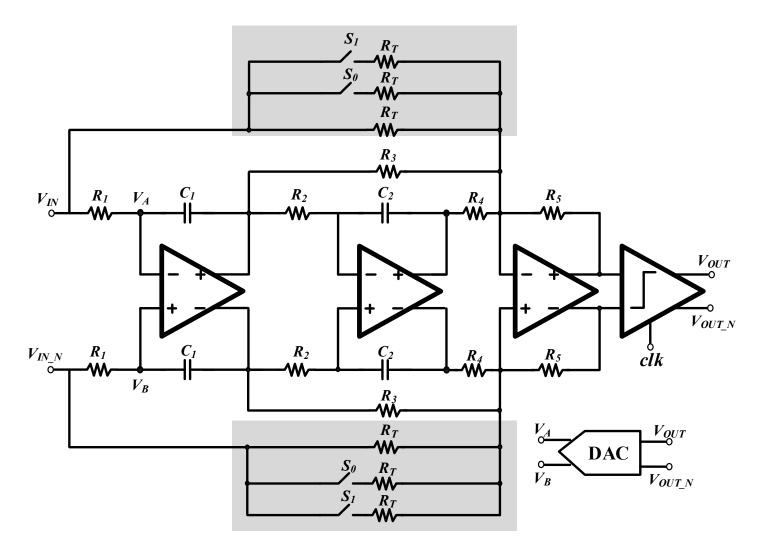

| 5.8  | Continuous-time Fully Differential $2^{nd}$ -order $\Delta\Sigma$ modulator with gain |    |

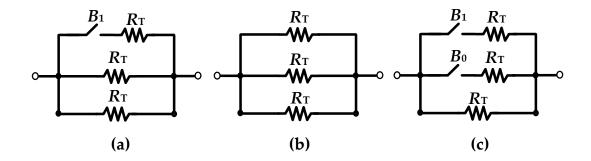

|      | compensation technique                                                                | 94 |

| 5.9  | Gain compensation technique (a) normal condition, (b) gain increasing,                |    |

|      | and (c) gain decreasing                                                               | 95 |

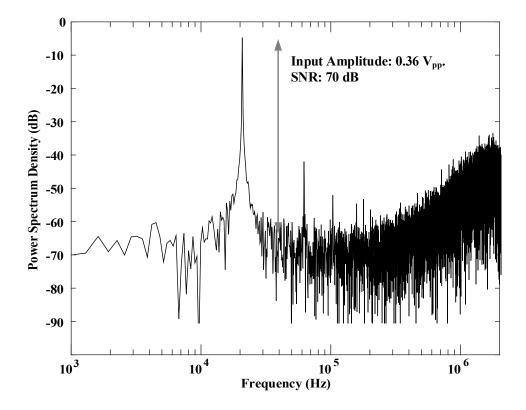

| 5 10 | Power spectrum density of the modulator.                                              | 96 |

### List of Figures

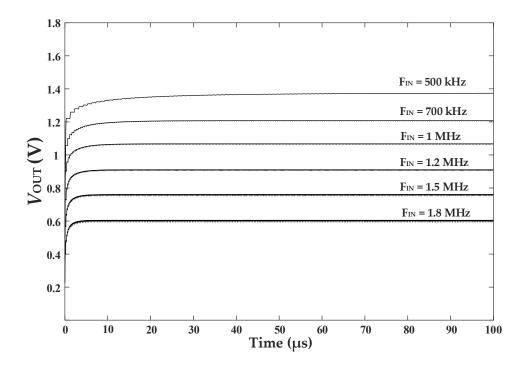

| 5.11 | Output characteristic of the frequency-to-DC converter against frequency            |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | sweeping                                                                            | 97  |

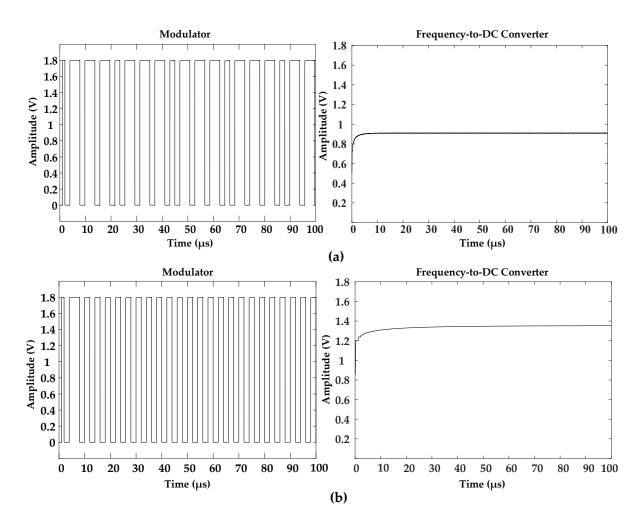

| 5.12 | Transient waveform of the modulator and converter where (a) fault-free              |     |

|      | and (b) catastrophic condition                                                      | 98  |

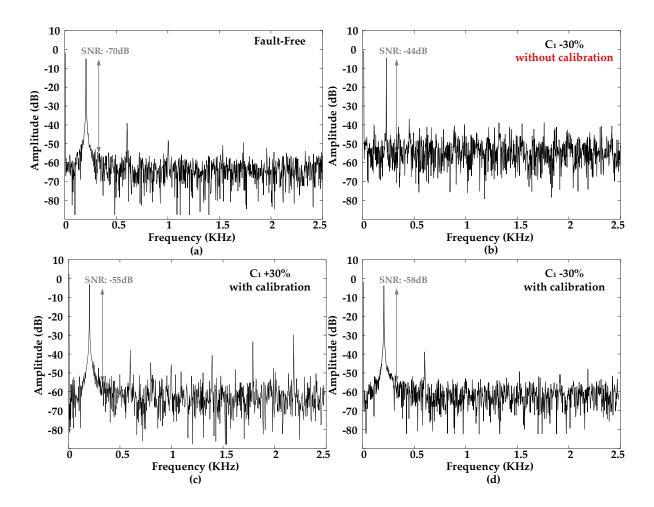

| 5.13 | Demonstration of the calibration of SNR in difference circuit conditions            |     |

|      | (a) fault-free, (b) $+30\%$ in $C_1$ without calibration, (c) $+30\%$ in $C_1$ with |     |

|      | calibration, and (d) -30% in $C_1$ with calibration                                 | 99  |

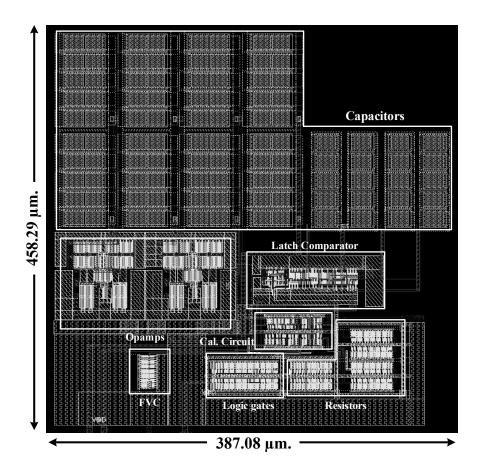

| 5.14 | Overall layout diagram of the proposed BIST and calibration technique.              | 100 |

# List of Tables

| 2.1 | Transistor aspect ratio of the designed $\Delta\Sigma$ modulator       | 30 |

|-----|------------------------------------------------------------------------|----|

| 2.2 | Summary of NIST standard test results of 1,000,000 binary sequences of |    |

|     | 30 proportions                                                         | 33 |

| 2.3 | Summary of Alphabit battery                                            | 34 |

| 2.4 | Summary of Rabbit battery                                              | 36 |

| 2.5 | Summary of significant performances and comparison to previous works.  | 37 |

| 2.6 | Summary Performances of the Proposed BIST                              | 43 |

| 3.1 | Summary performances of the OTA                                        | 59 |

| 3.2 | Transistor aspect ratio of the designed modulator                      | 59 |

| 3.3 | Summary performances of the $\Delta\Sigma$ Modulator                   | 60 |

| 3.4 | Summary of faults detectability of the DFST topology                   | 65 |

| 3.5 | Comparisons of this work and other related topology                    | 66 |

| 4.1 | Transistor aspect ratio of the operational amplifier                   | 80 |

| 4.2 | Summary of faults detectability of the proposed system                 | 82 |

| 4.3 | Summary of undetectable bands in the passive components                | 82 |

| 4.4 | Comparison of the testing time                                         | 83 |

| 5.1 | Comparison of the testing time                                         | 87 |

| 5.2 | Summary performances of the continuous-time $\Delta\Sigma$ modulator   | 96 |

| 5.3 | Summary of BIST performance                                            | 97 |

# Chapter 1

# Introduction

The demand of microelectronics devices has been growing doubly over the past two decades, due to the variety features of complementary metal oxide semiconductor (CMOS) process, i.e. low power, integration capability, and inexpensive manufacturing process. As a result, electronics industry has attempted to produces the devices at substantially lower cost per function with higher performance year after year. Scaling down the transistor size is the key factor of this issue. Otherwise, all dimensions of a CMOS transistor are scaled while preserving its behavior, yielding to larger amount of transistors and higher complexity integrated circuits (ICs). Every reduction of transistor size, cheaper and higher speeds of micro-processors are enabled. These developments lead to the evolution in numerous application domains such as communications, industry, and computer technology.

It is apparent that scaling down the transistors size into deeper sub-micron trends to proceed continuously. Likewise, the difficulty of design and manufacture has concurrently increased where the designing of perfect ICs seem to reach the unrealistic. For example, scaling a junction depths and gate oxide thickness may sustain the large variation of CMOS transistor parameters, resulting in unusual delays and leakage currents. These phenomenon occurs when more transistors are densely fabricated per unit area. In other words, number of transistors and wire have become larger, creating a larger area to sustain manufacturing defects. The transistor sizes have become smaller, increasing the volume and variety of defects during the fabrication process. Consequently, small

Fig. 1.1 Number of defects versus transistor shrinking size.

defects and imperfections are created during the manufacturing process and cause the failure circuits. Fig. 1.1 shows the number of defects during the manufacturing process versus transistor shrinking size. It can be clearly seen that deeper sub-micron technology causes higher number of defects in an exponential behavior. This issue necessitate the requirement of reliable ICs. Testing has become an important part to improve the quality and reliability of manufacturing ICs process, which has widely gained an attention on either research and industrial area.

This chapter introduce the necessary issue, beginning with the necessary of testing in an integrated circuit design. Underlying of defects in the realistic ICs production is lately described. Afterward, classification of testing architectures are briefly presented. The objective and organization of this dissertation are also described in the end of chapter.

Fig. 1.2 The role of analog circuits in overall electronically process.

#### 1.1 An overview of Mixed-Signal Testing

Sound, temperature, light density and velocity are dynamically quantities. Such a natural phenomenon is continuously varying in terms of magnitude and time. Processing these information from environment needs the advantages of an analog and digital system. The role of analog circuits is dealing with the input signals directly such as amplifying, filtering and converting. While digital circuits operate the analog signals logically at discrete intervals and generate the result values. The output of the system may be converted back to the natural signals by analog circuits at the end of process. Fig. 1.2 depicts the role of analog circuits in overall electronically process. The analog circuit is the interface between natural information and digital system which may be defined as a pre/post-processing part in the electronically process. This integration of analog and digital system in single device is called mixed-signal system, which is widely

#### 1.2 Defects in the Integrated Circuits

used in modern applications.

Testing in the mixed-signal system is often operated in the individual part, i.e. analog and digital. In digital circuits, the input and output signals are realized in terms of logical (Boolean) and the performance is controllable depending on a programming language constructs. Test strategy can be simply designed by storing the binary distinction patterns in the memory. Unlike digital systems, analog systems are mainly nonlinear and their performance is determined by circuit parameters. Such behavior is complex and difficult to design the pass/fail conditions in terms of logical. Analog circuits also heavily suffer from process variation which can cause unacceptable performance degradation. Therefore, analog circuits is further susceptible to defects owing to the time and voltage continuous nature of their operation. Test complexity is the main issue of analog circuits where the proper test strategy are needed to discriminate between various pattern of faulty conditions and the fail-free condition.

#### 1.2 Defects in the Integrated Circuits

Defects can be classified into two categories, i.e. local and global. The local defects randomly occur within an IC, while the global defects distribute and affect in complete region of a wafer. This research deal with the local defects, which regularly caused by tiny dust, imperfection of fabrication process, etc. Some defects arise from process variability such as implantation and diffusion process. Fig. 1.3 illustrates a sample of defect types during the manufacturing process. The effect of defects on the circuit performance depends on a size and area of distribution. In other words, a single large particle may cause a short or open faulty circuitry, while a vast distribution of tiny particle may unaffected apparently. However its may cause a deviation in specifications, e.g. delay, gain error, current leakage, etc. Hence, the faults in ICs can be classified as

Fig. 1.3 Sample of defects in manufactured ICs.

a catastrophic or parametric. The catastrophic or hard faults are occurred by random large defects during the implantation or diffusion process causing an open, short, extra

Fig. 1.4 Basic BIST architecture.

device and missing functional behavior of the IC. On the other hand, the parametric or soft faults are due to small defects that too minor to cause hard faults, which slightly deviates the circuit parameter from their designed value.

The parametric faults is a crucial issue in the ICs testing process, due to unpredictable and practically undetectable with the ordinary testing methods. In addition, modeling of parametric faults seem to be an unrealistic, especially in analog circuits. Detection of this fault requires a complex algorithm and high accuracy measurements, which directly impact to the testing cost. Therefore, modern ICs design is aims to reduce these troubles and become a challenge.

#### 1.3 Brief Classification of Testing Architecture

The integrated circuits are very large variations in property, structure and performances, so specific testing methods are required in each sub-circuit. As mentioned in previous section, faults detection in analog circuits is relatively difficult because no accepted analog fault model exists. However, almost system-on-chips (SOC) contain not only the analog circuit but also digital portions such as analog-to-digital converter (ADCs), digital-to-analog converters (DACs), phase-locked-loops circuits, etc. Such cir-

#### 1.3 Brief Classification of Testing Architecture

cuits are defined as a mixed-signal circuit. There are many techniques for mixed-signal testing depending on specialized approaches which is integration of digital testing stimulus and parametric measurements. Two major issue for mixed-signal testing are (1) fully on-chip digital/analog test instruments and (2) reduce testing cost though an auto-test equipment (ATE). For this reason, built-in self-test (BIST) technique has widely been studied and utilized in modern mixed-signal circuits.

The underlying idea of BIST is to designing a system that can automatically test itself and return a response in term of "good" or "bad" (fault-free or faulty circuit). The general functionalities are a capable of generating test patterns and correctly perform a test response of the CUT. Consequently, specific circuits are required for providing a test function that can determine whether the CUT covered by BIST circuits are working properly or faulty. Fig. 1.4 depicts the architecture of BIST circuitry includes five essential functions. The two major functions comprise the test pattern generator (TPG) and the output response analyzer (ORA), that provides pattern stimulus for testing and indicate the output response of the CUT into type of pass or fault, respectively. The other two additional functions are test controller and input isolation that are necessary to facilitate execution of self-testing feature. The two distinctive features of BIST cover vertical testing ability and high diagnostic resolution. In the other words, it can be used at all levels testing, i.e. wafer and device-level testing, manufacturing testing, as well as system-level testing. When BIST circuits are enabled in the CUT, the output response indicates not only whether the faults exist in that VLSI device, but also identify the position of faulty circuit in some structure. Whereas designing the proper BIST circuits are reasonably a challenge that the CUT is operated without interference from the BIST circuit. Therefore, the two systems must be designed at least, i.e. a BIST and intended system which both systems must synchronously work together.

#### 1.4 Objectives of this Dissertation

The three major keys in the realization of an IC involves design, fabrication and testing. These three steps should be perfectly balanced in order to achieve the high quality ICs. For example, the test should cover all the likely defects in the design and should avoid the degradation of their design performance, or the design should work within the constraints of the process.

Therefore, this dissertation focuses on the development of new BIST techniques, which a capable of high faults detection including catastrophic and parametric faults. The design strategy is to improve the basic building blocks of BIST, i.e. test stimulus generation, test control, and test response analyzer. All designed BIST is expected to avoid the system performance degradation and to distinguish between good and faulty ICs completely on-chip. The contributions of this dissertation arise from a design of compact and high-speed test stimulus generator, which can reduce the area requirement of BIST circuitry and testing time process. Second, a self-testability system without the stimulus generator is presented in terms of a oscillation-based testing. The proposed system offers a non-instructive source and cover all significant faults in tested ICs. Finally the concept of self-test and calibration is introduced with a capability of preserving an important functional of faulty circuits.

#### 1.5 Dissertation Organization

This dissertation is organized into six chapters. The following chapter 2 presents a full-custom design of chaos-based True Random-Bit Generator (TRBG) implemented on a 0.18- $\mu m$  CMOS technology with unique composition of three major components, including (i) chaotic jerk oscillator, (ii)  $\Delta\Sigma$  modulator, and (iii) simple pre/post-processing. A high-frequency all-CMOS chaotic jerk oscillator has been employed as

#### 1.5 Dissertation Organization

a source of randomness. Dynamics properties are described in terms of bifurcation diagram and the Largest Lyapunov Exponents (LLEs) spectrum. The continuous-time  $2^{nd}$ -order  $\Delta\Sigma$  modulator has firstly introduced for an increase in a resolution of random bit sequences while an extra clock is not required. Detailed circuit designs for both chaotic jerk oscillator and  $\Delta\Sigma$  modulator will be described and the standard statistical measure of randomness will be performed using NIST SP800-22 test suite. The designed chaotic oscillator is utilized as a testing stimulus generator, which can generate testing stimuli automatically and suitable to implement on a single-die chip. Faults detection is achieved through the simple method without requiring any additional digital processing units.

Chapter 3 presents an alternative topology of structural-based testing for the discrete-time  $\Delta\Sigma$  modulator. The structure of circuit-under-test is modified and operated as two symmetric structure circuits in the test mode. Different DC offset and simple digital counters are connected to the input and output of the circuit in order to reduce testing process complications and costs, with the modulator operated as a simple signal generator in the test mode. A demonstration of the testing process is performed through the switched-capacitor second-order  $\Delta\Sigma$  modulator, which achieves several advantages, including low cost, high-speed testing, and high fault coverage, and covers parametric failure.

Chapter 4 presents the BIST based on a phase difference analysis technique for the analog circuits. The test operation is achieved through the detection of phase shifting between two signals (i.e. the circuit-under-test and the reference clock). The faults signature is simply generated, and diagnosed by digital circuits, including a counter and basic logic components. The test stimulus generation and pass/fail decision are accomplished entirely on-chip, and also offers the range of tolerance in the passive analog components with eliminating the need for the external test equipment.

#### 1.5 Dissertation Organization

The BIST method with self-calibration feature for the continuous-time  $\delta\sigma$  modulator is introduced in chapter 5. This chapter initially reviews the conventional oscillation testing approaches, and calibration schemes in mixed-signal circuits. The simple circuitry such as a frequency-to-DC circuit, a windows comparator, and basic logic elements are utilized as the faults detection circuits. The calibration system is additionally implemented through the resistor array with a feedback network in order to adjust the gain value of the CUT. Simulation results show the capable of faults detection involves catastrophic and parametric variation. Moreover, the signals-to-noise ratio (SNR) of the CUT can be preserved at the acceptable level against the failure circuitry.

Finally, chapter 6 conclude the overall proposed techniques. The advantages and discussion of all techniques are given. Some potential research directions are recommended as well.

# Chapter 2

# True Random Bit Generator for High-Speed Testing in $\Delta\Sigma$ Modulator

This chapter presents a full-custom design of chaos-based True Random-Bit Generator (TRBG) implemented on a 0.18- $\mu m$  CMOS technology with unique composition of three major components, including (i) chaotic jerk oscillator, (ii)  $\Delta\Sigma$  modulator, and (iii) simple pre/post-processing. A high-frequency all-CMOS chaotic jerk oscillator has been employed as a source of randomness. Dynamics properties are described in terms of bifurcation diagram and the Largest Lyapunov Exponents (LLEs) spectrum. The continuous-time  $2^{nd}$ -order  $\Delta\Sigma$  modulator has firstly introduced for an increase in a resolution of random bit sequences while an extra clock is not required. Detailed circuit designs for both chaotic jerk oscillator and  $\Delta\Sigma$  modulator will be described and the standard statistical measure of randomness will be performed using NIST SP800-22 test suite. The compact chaotic oscillator is utilized as a testing stimulus generator, which can generate testing stimuli automatically and suitable to implement on a single-die chip. Faults detection is achieved through the simple method without requiring any additional digital processing units.

# 2.1 Review on the conventional True Random Bit Generator

Random Bit Generator (RBG) is typically achieved by software-based such as a Linear Congruential Generator (LCG), a Lagged Fibonacci Generator (LFG), and a Linear-Feedback Shift Register (LFSR). As the algorithm-oriented, most of the software-based RBG is defined as a pseudo- random generator, which the randomness is limited by the source generation, resulting in the existence of periodic intervals in the output sequences. Hardware True Random-Bit Generator (TRBG) is a physical process that typically provides a random sequence in which values of bit streams are uniformly distributed over a definite set, and cannot be reliably predicted based on the existing set of values [1]. The hardware TRBG generally represents fundamental cryptographic primitives, and therefore stringent requirements, such as unpredictability and proven statistical standard properties, must be satisfied in order to assure robustness and resistance against attacks [2]. As advanced technologies and expeditious computation have rapidly emerged, the need for robust and high-speed hardware TRBGs has consequently received considerable attention in order to support modern applications such as in security of parallel computing or in real-time data encryptions. [3, 4, 5]

Classical hardware TRBGs are based on stochastic systems that exploit physical phenomenon as sources of randomness such as a jitter noise of clock signals and metastability in circuits [6, 7, 8] or thermal or shot noises obtained from analog devices [9, 10]. However, those classical hardware TRBGs require a properly customized circuitry for randomness extraction. On a contrary to stochastic systems, chaos-based hardware TRBGs are based on a deterministic system in which a source of randomness can be obtained from a well-defined mathematical model, and hence deterministic chaotic circuit. On the one hand, several techniques for chaos-based hardware TRBGs

#### 2.1 Review on the conventional True Random Bit Generator

have recently been proposed through the utilization of Field Programmable Gate Array (FPGA) [11, 12, 13]. Nonetheless, the FPGA is an independently external device that requires an interface to other application processes, and the design process of TRBGs on FPGA is highly complicated due to the proper optimization among various aspects, involving a slice area, RAM, processing speed. Remarkably, the implantation of TRBGs on FPGA is critically depends on a clock frequency, which is a major limitation for gaining high data rate and throughputs.

As an alternative to FPGA, the implementation of chaos-based TRBGs in Application-Specific Integrated Circuit (ASIC) has also received much interest due to a completely embedded security module in physical layer applications. On the one hand, TRBGs based on 3-dimendtional chaotic flow have been reported in two categories, i.e. (i) autonomous flows, including Lorenz [14] and Chen's systems [15], and (ii) non-autonomous flows, involving a sinusoidal-forced [16] and triangle-wave-based LC chaotic oscillators [17]. These types of TRBGs, however, has a limitation on low output data rate as chaotic flow naturally provides low frequency outputs unless a complex post-processing is exploited. On the other hand, TRBGs based on 1-dimendtional chaotic maps have extensively been proposed such as those of utilizing Bernoulli shift map [18], Sawtooth map [19], or Approximate V-shape map [20]. Despite the fact that chaotic maps are simple in terms of circuit implementation and capable of generating higher frequency than that of chaotic flows, either switched-capacitor [21] or switched-current [22] are essentially required and hence a clock frequency becomes a critical issue as FPGA.

Recently, attempts for implementing high-speed and high-data-rate chaos-based TRBGs based on Analog-to-Digital Converters (ADC) as an interface between a source of randomness and a post-processing unit have been suggested. The modified multi-stage pipeline ADCs as a chaotic source using 0.18- $\mu m$  CMOS based TRBGs [23] provides

#### 2.1 Review on the conventional True Random Bit Generator

Fig. 2.1 The proposed circuit configuration of chaotic jerk oscillator.

an output rate of 40 Mbit/s and another TRBGs constructed by a Photonic Integrated Circuit (PIC) that emits broadband chaotic signals provides extremely high data rate of 140 Gb/s [24]. Despite a high data rate, the multi-stage pipeline ADCs is complicated requiring a number of components whilst the PIC is expensive and suitable for specific applications such as in communication systems.

#### 2.2 An Autonomous Chaotic Jerk Model

An autonomous chaotic system has been an active subject in the fields of physics since the first discovery by Lorenz in 1963 [25]. The system has illustrated by a set of third-order ordinary differential equations (ODE), showing in the three-dimensional phase-space domain and requires at least one non-linearity function. In addition, an explicit form of third-order ODE has been reported in 1996 [26], called "jerk function". It can be written as  $\ddot{x} = J(x, \dot{x}, \ddot{x})$ , which represents the derivative of acceleration. The jerk form of chaotic systems has gained great attention due to its showing in the form of the single dynamical system. The particular advatage of a jerk form is a capability of investigating chaotic dynamics through damping coefficients in a single equation.

Although the chaotic dynamics can be analyzed regarding numerical and demonstrated by a computational tool, the appropriate condition for ensuring the chaotic phenomenon in real nature is to implement in electronic devices. Several approaches have been investigated the simple term of chaotic jerk equations [27, 28, 29] in order to minimize the circuit components. However, even simple jerk equation may lead to a complex circuit due to the non-linearity function, e.g., an exponential, absolute and power function [30, 31, 32].

The simple model of chaotic jerk system with double-score-like behavior is presented in this Section. Implementation of CMOS architecture with adjustable attractor feature is also described through the numerical analysis and simulation in the circuit level.

#### 2.2.1 All-CMOS Chaotic Jerk Oscillator

A typical chaotic jerk oscillator is a three-dimensional chaotic system, and can generally be described by a mathematical model in the case where a nonlinear function is in an x term with first-order polynomial included as follows

$$\ddot{x} = a_6 \ddot{x} + a_5 \dot{x} + a_4 x + a_3 f (a_2 x + a_1) + a_0 \tag{2.1}$$

where  $a_i$ , i = 0, 1, 2...6, is a coefficient. Based upon Eq. (2.1), Fig. 2.1 subsequently depicts a realization of a simple all-CMOS chaotic jerk oscillator through inherently hyperbolic tangent nonlinearity in an operational amplifier (Opamp). It can be considered in Fig. 2.1, two essential building blocks are (i) the three consecutive integrators for composition of a third-order chaotic flow, and (ii) a differential amplifier that inherently provides Hyperbolic Tangent (tanh) nonlinearity. Additionally, a transducer and a current-mirror circuit are necessarily required in order to fulfill chaos dynamics. As for circuit simplicity purposes, on the one hand, most building blocks were implemented based on a simple inverter comprising a typical complementary nMOS and pMOS. The inverter operating in a saturation mode typically provides a transconductance gain  $G_m$  as follows

$$G_m = \mu_n C_{OX} \frac{W_n}{L_n} \left( V_{GS} - V_{THn} \right) + \mu_p C_{OX} \frac{W_p}{L_n} \left( V_{GS} - V_{THp} \right)$$

(2.2)

where  $\mu_n$  and  $\mu_p$  are electron mobility of nMOS and pMOS transistors respectively.  $C_{OX}$  is an oxide capacitance. W and L are width and length of a transistor. The voltage  $V_{GS}$  is a gate-source voltage of a transistor. The voltages  $V_{THn}$  and  $V_{THp}$  are threshold voltages of nMOS and pMOS transistors, respectively. On the other hand, the differential amplifier employs two nMOS transistors  $N_9$  and  $N_{10}$  as a differential input pair, and exploits two pMOS transistors  $P_9$  and  $P_{10}$  as an active load in a current-mirror configuration in order to provide a single-ended output. Assuming a differential input pair is operated in a saturation region, the voltage-to-current transfer characteristics, i.e.,  $i_{out} = f(v_{in})$ , can approximately be described in piecewise-linear nonlinear model using the square law as follows

$$i_{out} = \begin{cases} \frac{1}{2} \mu_n C_{OX} \frac{W_9}{L_9} V_i \sqrt{2K^2 - v_{in}} &, |v_{in}| \le K \\ I_{DC} sgn(v_{in}) &, |v_{in}| > K \end{cases}$$

(2.3)

Fig. 2.2 Plots of the spectrum of LLEs and Bifurcation diagram of  $X_{max}$  over a tuning voltage  $V_T$ .

where  $sgn(v_{in})$  is a Signum function and K is a constant defined as

$$K = \sqrt{\frac{2I_{DC}}{\mu_n C_{OX} \frac{W_9}{L_9}}} \tag{2.4}$$

For purpose of simplicity, the values of W and L of both pMOS and nMOS transistors were set to be equal, and hence the transconductance  $G_m$  is therefore equal for all inverters. A mathematical model of the proposed CMOS chaotic jerk oscillator in Fig. 2.1 can be formulated through a classical circuit analysis using Kirchhoff's law, and the results reveal the system of Ordinary Differential Equations (ODEs) as follows

$$\frac{dv_x}{dt} = -\frac{G_m}{C_x}v_y$$

$$\frac{dv_y}{dt} = -\frac{G_m}{C_y}v_z$$

$$\frac{dv_z}{dt} = -\frac{G_m}{C_z}v_x + \frac{G_m}{C_z}v_y - \frac{G_m}{C_z}v_z + \frac{f(v_x)}{C_z}$$

(2.5)

Fig. 2.3 Chaotic waveform in time-domain of (a)  $v_x$ , (b)  $v_y$ , and (c)  $v_z$  at  $V_T = 0.9V$ .

where the nonlinear function  $f(v_x)$  is a hyperbolic tangent function expressed as

$$f(v_x) = I_{DC} tanh \left(b_1 \left(b_2 v_x - V_T\right)\right) \tag{2.6}$$

where a constant  $b_1$  is a scaling factor of a typical tanh function while a constant  $b_2$  a voltage gain. In this particular design, the capacitor  $C_z$  is unique while the capacitors

Fig. 2.4 Two-dimensional strange attractor with different tuning the voltage  $V_T$  obtained from the proposed oscillator, between (a-c)  $v_x$  -  $v_y$ , (d-f)  $v_x$  -  $v_z$ , (g-i)  $v_y$  -  $v_z$ .

$C_x$  and  $C_y$  are equal, and therefore  $C_{xy}$  is denoted in a manner that  $C_{xy} = C_x = C_y$ . The time constant  $\tau = C_{xy}/G_m$ . The system characteristics can be changed by the DC tuning voltage  $V_T$ . A dimensionless system of Eq. (2.5) is summarized in a matrix form described in Eq. (2.7), comprising normalized variables (X, Y, Z), system constants (A, B, C), and an arbitrary reference voltage  $V_r$ .

$$\begin{bmatrix} \dot{X} & X & A \\ \dot{Y} & Y & B \\ \dot{Z} & Z & C \end{bmatrix} = \begin{bmatrix} \frac{dX}{d\tau} & \frac{v_x}{V_r} & \frac{C_{xy}}{C_z} \\ \frac{dY}{d\tau} & \frac{v_y}{V_r} & \frac{C_{xy}I_{DC}}{G_mV_rC_z} \\ \frac{dZ}{d\tau} & \frac{v_z}{V_r} & \frac{V_T}{V_r} \end{bmatrix}$$

$$(2.7)$$

Fig. 2.5 Poincarè mapping in planes where (a)  $v_z = 0.84$ , (b)  $v_y = 0.84$ , and (c)  $v_x = 0.84$ .

$$\begin{bmatrix} \dot{X} \\ \dot{Y} \\ \dot{Z} \end{bmatrix} = \begin{bmatrix} 0 & -1 & 0 \\ 0 & 0 & -1 \\ -A & A & -A \end{bmatrix} \begin{bmatrix} X \\ Y \\ Z \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ Btanh(b_1(b_2X - C)) \end{bmatrix}$$

(2.8)

Transformation of a dynamical form in Eq. (2.8) into a jerk equation results in a following form

$$\ddot{X} = -A\left(\ddot{X} + \dot{X} + X\right) + Btanh\left(b_1b_2X - b_1C\right) \tag{2.9}$$

Eq. (2.9) also apparently satisfies mathematical model as previously described in a generic jerk form in Eq. (2.1) with following coefficients, i.e.,  $a_6 = -A$ ,  $a_5 = -A$ ,  $a_4 = -A$ ,  $a_3 = B$ ,  $a_2 = b_1b_2$ ,  $a_1 = b_1C$ , and  $a_0 = 0$ .

#### 2.2.2 Chaotic Dynamics Evaluation

In order to investigate chaotic dynamics from the proposed oscillator, solutions of the jerk Eq. (2.9) were simulated in MATLAB using the  $4^{th}$ -order Runge-Kutta integration algorithm with a step size of  $10^{-3}$  and the initial condition was set at (0.01, 0, 0). The parameters  $W_n$  and  $L_n$  of all nMOS transistors are  $1\mu$ m and  $0.36\mu$ m, respectively. Meanwhile, the parameters  $W_p$  and  $L_p$  of all pMOS transistors are  $2.4\mu$ m and  $0.36\mu$ m, respectively. The resulting transconductance of inverters  $G_m$  is equal to  $288\mu$ S. The capacitors were specifically customized to  $C_{xy} = 10$ pF and  $C_z = 20$ pF. The DC current was set to  $I_{DC} = 26\mu$ A. The constant parameters  $b_1$  and  $b_2$  were appropriately fixed to 500 and 15, respectively. A bifurcation diagram of  $X_{max}$  and

Fig. 2.6 Block diagram of the proposed TRBG with  $\Delta\Sigma$  modulation of chaotic jerk signals.

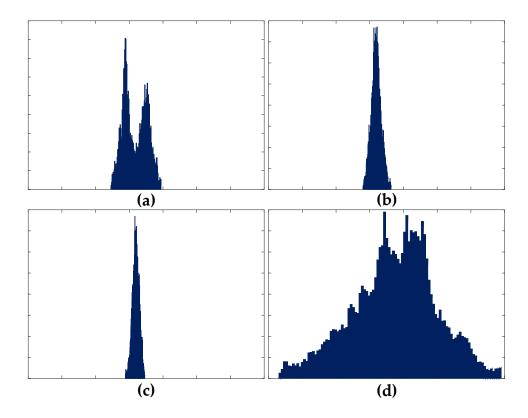

Fig. 2.7 Histograms of the chaotic jerk signals at (a)  $v_x$ , (b)  $v_x$ , (c)  $v_x$ , and (d) after scrambling process.

LLEs spectrum were simulated, as a qualitative and quantitative measurements, by tuning the voltage  $V_T$  from 0.15V to 1.65V in 1,000 steps. The LLEs is a quantity that characterizes the rate of separation of infinitesimally close trajectories, expressed as

$$LE = \lim_{n \to \infty} \frac{1}{N} \sum_{n=1}^{N} log_2 \frac{dX_{n+1}}{dX_n}$$

(2.10)

Fig. 2.8 Block diagram and a circuit of the signals scrambling technique.

where N is the number of iterations. Fig. 2.2 illustrates the bifurcation diagram of  $X_{max}$  against voltage  $V_T$ , where the variety of dynamics are obviously exhibited on the dense region (0.3 - 1.38). In addition, the chaotic dynamics in such region are also indicated by the positive values of the LLEs spectrum. Fig. 2.3 shows signals waveform in time-domain of  $v_x$ ,  $v_y$  and  $v_z$  at  $V_T = 0.9V$ , which apparently exhibit a nonlinear behavior.

In addition, the proposed CMOS chaotic jerk oscillator has been implemented using Cadence virtuoso environment with 0.18- $\mu m$  Rohm CMOS technology. Fig. 2.4 shows the balanced-to-unbalanced transition of double-scroll attractors on node  $v_x$  -  $v_y$  (a-c),  $v_x$  -  $v_z$  (d-f), and  $v_y$  -  $v_z$  (g-i), where the tuning voltage  $V_T$  is varied from 0.7V to 1.05V. Fig. 2.5(a), (b), and (c) show the Poincarè mapping in 2-dimensional plane where  $v_z = 0.84$ ,  $v_y = 0.84$  and  $v_x = 0.84$ , respectively. The tuning voltage  $V_T$  is set to 0.9. It is noticeable form the trajectories that this system exhibits the symmetrically double-scroll dynamics with the equilibrium point at 0.84V. It is clearly seen that the proposed oscillator is a capable of an autonomous generating smooth transitions from a balanced double-scroll jerk attractor to an unbalanced double-scroll, and additionally to either a right-half or a left-half single-scroll attractor by varying a DC tuning voltage. The proposed CMOS chaotic jerk oscillator operates at 1.8-V single supply voltage and

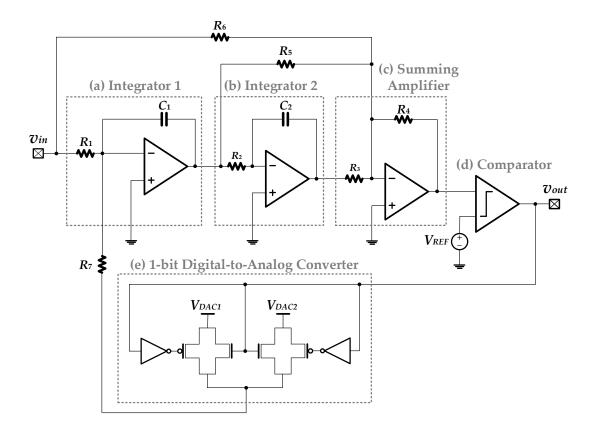

Fig. 2.9 The single-bit second-order  $\Delta\Sigma$  modulator with feed-forward topology.

the power dissipation is 0.72 mW.

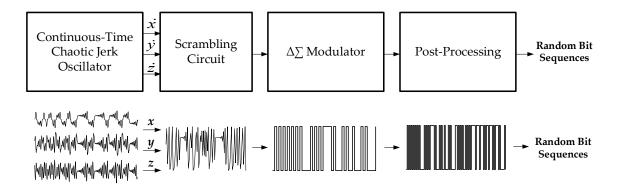

## 2.3 Proposed Architecture of a TRBG through $\Delta\Sigma$ Modulation of Chaotic Jerk Signals

The overall system of the proposed TRBG with  $\Delta\Sigma$  modulation of chaotic signals is illustrated in Fig. 2.6. The system comprises four important components, i.e. the continuous-time chaotic jerk oscillator, a simple scrambling signals circuit, a  $\Delta\Sigma$  modulator, and a post-processing circuit. The non-deterministic chaotic signals are generated automatically by the chaotic jerk oscillator as the source of the TRBG. Utilization of the chaos-based oscillator has gained numerous advantages such as elimination a complex structure of the signal generators, a nondeterministic entropy source, and the truly

Fig. 2.10 (a) Folded-cascode operational transconductance amplifier and (b) a dynamic comparator.

randomness property based on physical phenomenon. However, a crucial issue is the synchronization property of chaotic dynamics, i.e. the behavior of two or more chaotic systems, either equivalent or nonequivalent, might be synchronized by linking them with common signals [33].

The output sequences might be predicted by a mimic system using master-slave synchronization scheme [34]. Thus, a pre/post-processing method is necessary for TRBG in order to fulfill the imperfections of the chaotic property. The chaotic signals of each output nodes  $(v_x, v_y, v_z)$  are merged together by the scrambling circuit as a simple pre-processing technique. Lastly, the randomness of binary sequences is enchanted by the digital post-processing stage based on the structure in [35].

In order to increase the data rate, the continuous-time  $\Delta\Sigma$  modulator is employed with high sampling frequency. Oversampling property is the major key to achieve the higher transmission rate. Otherwise, using an embedded quantizer in a feedback loop and applying a signal processing technique, therefore increasing the output resolution. This section presents an architecture of the proposed TRBG in terms of the circuit realization. The overall circuits are implemented on 0.18- $\mu$ m CMOS standard technology.

Fig. 2.11 Output power spectrum density of the modulator.

Fig. 2.12 Signal-to-noise ratio as a function of normalized input power.

Fig. 2.13 Layout diagram of overall circuits in 0.18- $\mu$ m CMOS standard technology.

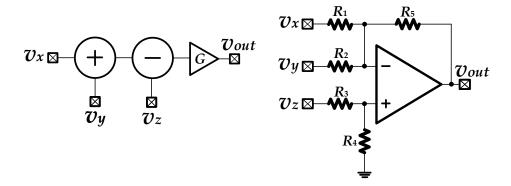

#### 2.3.1 Signals Scrambling Circuit

A scrambling signals technique is typically utilized in a secure communication system in order to avoid the periodic data and to smoothly combine the frequency smoothly over the available bandwidth. Fig. 2.7(a), Fig. 2.7(b), and Fig. 2.7(c) show the output histogram of the chaotic jerk oscillator at nodes  $v_x$ ,  $v_y$ , and  $v_z$ , respectively. It is clearly seen that the amplitude of each node is indicated in the narrow range of bandwidth (less than  $0.4V_{pp}$ ), which is undesirable for the TRBG. Therefore, the scrambling technique is used, as the pre-processing method, to intergrade the three output nodes  $(v_x, v_y, v_y, v_z)$  and  $v_z$ ) into a single output node, and expand the amplitude range of the chaotic jerk oscillator. The method is achieved by the three operations, i.e. summing, subtraction, and amplifying, and can be implemented by a simple circuit. Fig. 2.8 depicts a block diagram and a circuit of the proposed scrambling technique, where  $R_1 = R_2 = R_3 = R_A$  and  $R_4 = R_5 = R_B$ , the output of the circuit can be expressed as

$$v_{out} = \frac{R_B}{R_A} \left[ (v_x + v_y) - v_z \right]$$

(2.11)

Fig. 2.7(d) illustrates the output histogram after scrambled signals, when  $R_A$  and  $R_B$  are fixed as  $20k\Omega$  and  $50k\Omega$ , respectively. The histogram indicates higher distribution of the output amplitude, which is a require property of the TRBG.

#### 2.3.2 The Continuous-Time $\Delta\Sigma$ modulator

Unlike a discrete-time system, which the switched-capacitors is a major component for sampling operation, the continuous-time design places the input sampling just before the quantizer. Consequently, a non-overlapping clock generator is not required and the system throughput can be determined by maximum sampling rate of the quantizer (comparator). Without the switched-capacitors, the continuous-time consume less power than the discrete-time system and also easy to drive form external input with high bandwidth. Fig. 2.9 shows the second-order continuous-time  $\Delta\Sigma$  modulator with feed-forward topology. The circuit comprises two RC integrators, a summing amplifier, a comparator as 1-bit quantizer, and 1-bit digital-to-analog converter (DAC). The feed-forward topology is used in order to decrease a harmonic distortion and increase a signal-to-noise ratio (SNR). The output of the modulator in z-transform is given by

$$v_{out}(z) = \frac{v_{in} \left[ z^{-2} \left( a_1 a_2 c_1 - a_1 c_2 \right) + a_1 c_2 z^{-1} \right] + Q \left( 1 - z^{-1} \right)}{z^{-2} \left( a_1 a_2 c_1 - a_1 c_2 + 1 \right) + z^{-1} \left( a_1 c_2 - 2 \right) + 1}$$

(2.12)

where Q(z) is the quantization error of the modulator. The parameter  $a_1$ ,  $a_2$ , and  $c_1$ ,  $c_2$  represent integrator gain and the feed-forward gain, respectively. The operational transconductance amplifier (OTA) is the core component whose implementation determines the performance of the  $\Delta\Sigma$  modulator. Basically, the dominant specifications that affect the modulator performance comprise the bandwidth, speed, and stability, where a 60dB DC gain is adequate. A two-stage OTA is commonly used with Miller compensation. This can provide a high speed and high output swing but suffers from a poor power-supply rejection ratio (PSRR) and high power consumption. Another

drawback is a difficulty in detecting parametric faults, which is due to the internal compensation components (e.g., resistor and capacitor). These limited performances can be compensated for by a folded-cascode OTA, which offers good input common-range, self-compensation, and high DC gain. A high-performance, folded-cascode OTA is utilized as illustrated in Fig. 2.10(a). The differential-output DC gain and the power dissipation can be given by

$$A_{DC} = \alpha \left( 1 + \lambda \right) \left( G_{mn} r_{DSn} \right) \tag{2.13}$$

$$P_{diss} = (I_3 + I_6 + I_7 + I_8) (V_{DD} + |V_{SS}|)$$

(2.14)

where  $\alpha$  and  $\lambda$  are the relative values of N- and P-transistor transconductance and the current flows in M<sub>8</sub>, respectively. The simulation results from HSPICE software implies that the designed OTA can achieve a unity gain bandwidth (GBW) more than 60MHz with load capacitance of 1pF and phase margin of 83°. The DC gain of the Opamp is higher than 64dB at  $30\mu$ A bias current and the measured power dissipation is approximately 0.19mW.

The comparator is the secondary major component that affects the modulator performance. The requirements of this block are flexible, since the performance of the modulator is nearly insensitive to the comparator offset and hysteresis function. The dynamic comparator with SR latch is considered as a single-bit quantizer, as shown in the Fig. 2.10(b). In order to achieve low power and high sampling rate, the circuit structure is designed based on Rahman et al. [36]. In this topology, symmetric structural with regenerative feedback is the major issue. This comparator dissipates at approximately 0.15mW with 50MHz of maximum sampling rate. The transistor aspect ratio of the overall sub-circuits is also shown in Table 2.1.

The performance of the proposed  $\Delta\Sigma$  modulator was validated through a HSPICE environment operated in the ordinary condition. The sinusoidal input at 1.785kHz was used with a 1MHz sampling frequency. Fig. 2.11 exhibits the simulated power spectrum

Fig. 2.14 Post-processing unit structure.

density (PSD) where a 65,536-points FFT with simple rectangular truncation window. The behavior of the SNR with of the input power is also shown in Fig. 2.12 where the maximum SNR was 96dB and almost reached 14 bits of the effective number of bits (ENOB). Meanwhile, the overall power consumption as measured was less than 0.6mW and dominated by the operational amplifier (0.19mW). It can be seen that the proposed  $\Delta\Sigma$  modulator achieves the power efficiency and acceptable performances widely found in commercial applications. Fig. 2.13 shows the layout diagram of overall circuits in 0.18- $\mu$ m CMOS standard technology.

## 2.3.3 Post-Processing Unit

Although, the chaotic-based entropy source provides a highly dynamic and unpredictable behavior, which are the applicable property of TRBG. However, the pure output of entropy source tends to be deviated from the true-randomness property over long-time. Therefore, the post-processing unit is typically required to reduce or remove such deviations, while still maintaining its generation bit-rate. Fig. 2.14 depicts the post-processing unit structure based on a Von Neumann Corrector [35]. The unit structure comprises four shift-registers which is connected by the Exclusive OR (XOR) logic operations. The delay stages (n) of the shift-registers is fixed to 8 and can be simply implemented by a Flip-Flop or latch. The XOR operation of the shift-register with

Table 2.1 Transistor aspect ratio of the designed  $\Delta\Sigma$  modulator.

| MO         | S Transistors                  | Aspect Ratio $(W/L)$ |

|------------|--------------------------------|----------------------|

|            | P <sub>1</sub> -P <sub>2</sub> | 180                  |

|            | P <sub>3</sub> -P <sub>4</sub> | 90                   |

|            | $P_5$                          | 296                  |

| Op Amp     | $N_1$ - $N_2$                  | 40                   |

|            | $N_3$                          | 20                   |

|            | $N_4$ - $N_7$                  | 80                   |

|            | $N_8$                          | 150                  |

|            | P <sub>1</sub> -P <sub>2</sub> | 12                   |

|            | P <sub>3</sub> -P <sub>4</sub> | 4                    |

| C .        | P <sub>5</sub> -P <sub>6</sub> | 12                   |

| Comparator | $N_1$ - $N_2$                  | 4                    |

|            | $N_3$ - $N_6$                  | 8                    |

|            | $N_7$                          | 12                   |

slightly different delay prevents an overlapping bits-pair (e.g., "0000" or "1111") and performs an equal amount of bit "0" and "1".

## 2.4 True Random Bits Generator Evaluation

Since the proposed TRNG is based on the chaotic source, the output bit sequences significantly imply the chaotic properties, which is a sensitivity to the initial condition, unpredictable, and deterministic. However, those properties do not indicate the randomness of the output bit sequences. The quality of TRBG typically depends on the statistical properties of the generated bit sequences, e.g. randomness, unpredictability, and correlation. In this section, entropy and two correlation testing methods have been used for a qualitative analysis. In addition, the most well-known quantitative method, i.e., the National Institute of Standards and Technology (NIST) Statistical Test Suite,

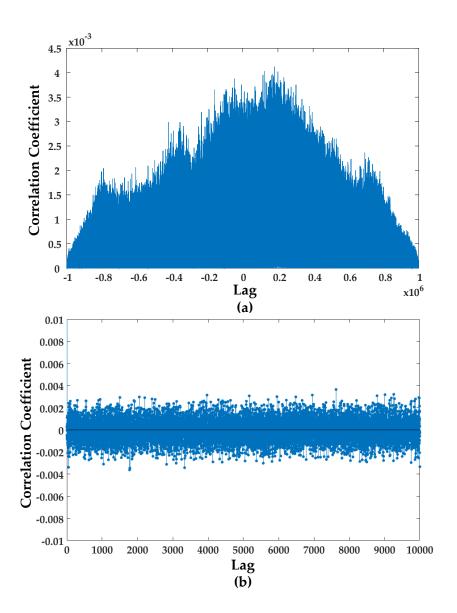

Fig. 2.15 Correlation analysis between the output binary sequences, (a) normalized cross-correlation, and (b) autocorrelation.

has been employed.

## 2.4.1 Cross-Correlation, Autocorrelation and Entropy

The cross-correlation function is a standard method for measuring the similarity between two time-series sequence. The input binary sequences are compared to identify a bit pattern that repeating in the time-series, known as a matching template algorithm.

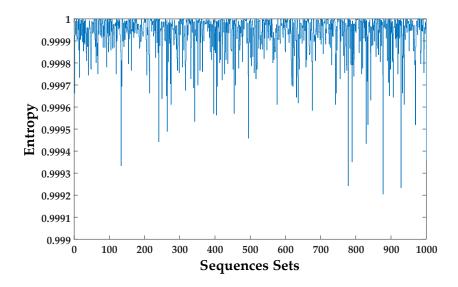

Fig. 2.16 The entropy of difference 1,000 sets of the output binary sequences.

The cross-correlation can be described as follows

$$r_{xy}(\tau) = \int_{-\infty}^{\infty} x(t) y(t+\tau) dt$$

(2.15)

where  $r_{xy}(\tau)$  represents a correlation coefficient of the time lags. The function x(t) and y(t) are the different time-series sequences. This function can also be normalized as

$$\overline{r}_{xy}(\tau) = \frac{|r_{xy}(\tau)|}{\sqrt{|r_{xx}(0)||r_{yy}(0)|}}$$

(2.16)

where  $\bar{r}_{xy}(\tau)$  is a normalized quantity in range -1 and 1. Likewise, an autocorrelation is the correlation with delayed between the value in the same time-series as follows

$$r_{xx}(\tau) = \int_{-\infty}^{\infty} x(t) x(t+\tau) dt$$

(2.17)

Typically, the unity value of correlation coefficient (r = 1) indicates the exactly similar at alignment of two time-series, whereas the r = 0 suggests that those sequences are uncorrelated together. Fig. 2.15(a) exhibits the normalized cross-correlation of two 1,000,000 binary sequences, where the autocorrelation of 1,000,000 binary sequences form the proposed system is shown in Fig. 2.15(b). It is apparent from the normalized cross-correlation and autocorrelation that the output binary sequences are practically

#### 2.4 True Random Bits Generator Evaluation

Table 2.2 Summary of NIST standard test results of 1,000,000 binary sequences of 30 proportions.

| Test Methods                                  | Proportion | P-values | Results |

|-----------------------------------------------|------------|----------|---------|

| Frequency Test                                | 1.00       | 0.6128   | Success |

| Block Frequency                               | 1.00       | 0.8254   | Success |

| Runs                                          | 1.00       | 0.2668   | Success |

| Longest Run of Ones Block                     | 1.00       | 0.9364   | Success |

| Binary Matrix Rank                            | 0.97       | 0.8626   | Success |

| Discrete Fourier Transform                    | 0.97       | 0.4517   | Success |

| Non-overlapping Template Matching (148 tests) | 1.00       | 0.4969*  | Success |

| Overlapping Template Matching                 | 0.97       | 0.7078   | Success |

| Universal Statistical                         | 1.00       | 0.3854   | Success |

| Linear Complexity                             | 1.00       | 0.6105   | Success |

| Serial 1                                      | 1.00       | 0.9828   | Success |

| Serial 2                                      | 0.97       | 0.2787   | Success |

| Approximate Entropy                           | 1.00       | 0.8535   | Success |

| Cumulative Sums (2 tests)                     | 1.00       | 0.7264*  | Success |

| Random Excursions (8 states)                  | 1.00       | 0.3077*  | Success |

| Random Excursions Variant (18 states)         | 1.00       | 0.3330*  | Success |

<sup>\*</sup> = Average P-values.

uncorrelated and rarely occurred the periodic region due to the correlation coefficients of two functions are relatively close to zero for entire values. Moreover, the entropy of thousand sets of 10,000 binary sequences have been investigated based on Shannon's entropy as illustrated in Fig. 2.16. As expected, the entropy values have reached the

Table 2.3 Summary of Alphabit battery.

| Test Methods                   | Parameter | Proportions |

|--------------------------------|-----------|-------------|

| $smultin\_MultinomialBitsOver$ | L=2       | 30/30       |

|                                | L=4       | 30/30       |

|                                | L=8       | 30/30       |

|                                | L=16      | 30/30       |

| ${\rm sstring\_HammingIndep}$  | L=16      | 30/30       |

|                                | L=32      | 29/30       |

| sstring_HammingCorr            | L=32      | 30/30       |

| $swalk\_RandomWalk1$           | L=64      | 30/30       |

|                                | L=320     | 30/30       |

unity for all sets of the output binary sequences which implies the high randomness property of entire sequences.

#### 2.4.2 NIST SP800-22 Standard Test Suite

The National Institute of Standards and Technology (NIST) has provided a high-acceptable statistical tests algorithm for specifically evaluate the randomness of binary sequences. In this paper, the widely-used NIST test suite from NIST SP800-22 [?] is utilized with typical 1,000,000 random binary sequences. The test suite comprises 15 test methods which imply the random characteristic of the sequences. Where the robustness of the perfect randomness is described by P-values (probability values), for example, a P-values greater than a level of 0.01 suggests that the tested sequences is performing the random behavior with 99% of confidential level. In the case of multiple random sequences, the acceptable proportion of passing sequences can be defined as follows

$$(1-\alpha) \pm 3\sqrt{\frac{\alpha(1-\alpha)}{k}} \tag{2.18}$$

#### 2.4 True Random Bits Generator Evaluation

where  $\alpha$  and k are the acceptable level of P-values and number of tested sequences, respectively. Table 2.2 summarizes the NIST test results of 1,000,000 binary sequences of 30 proportions, obtained from the proposed system. It can be clearly seen that the proportion of all testing methods are fall within the region of acceptable proportions (0.9355 – 1.044). Moreover, the P-values of overall testing methods were passed the acceptable level ( $\alpha = 0.01$ ), which implies that the proposed system is a potential to use as the truly random number generator.

#### 2.4.3 TestU01 Empirical Test Suite