## FPGA によるタイマー付きディジタル時計の設計および製作

# 電子・光システム工学科 矢野研究室 1080282 長野 真治

#### 1. はじめに

近年、ディジタル技術の発展により、加速的にディジタル化が進んでいる。本研究では、利用価値が高いと思われるキッチンタイマーを付加したディジタル時計をハードウェア記述言語の一つである VHDL を用いて設計し、FPGAを用いて製作した。

### 2. タイマー付きディジタル時計の設計

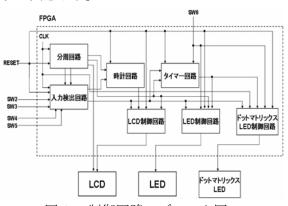

本研究では、キッチンタイマー機能を付加したディジタル時計を LCD に表示させ、同時に、タイマー残り 3 秒からドットマトリックス LED に表示させる回路を設計した。時計およびタイマーは、60 進カウンタと 24 進カウンタを用いて設計した。また、時計では 24 時間表示と 12 時間表示を切換可能なものとした。LCD 制御回路では、LCD 初期化データ送信後、表示データを送信するプログラムを設計した。LCD は、16文字×2行表示でLED バックライト付きのものを使用した。図 1 に、制御回路のブロック図を示す。

図1. 制御回路のブロック図

#### 3. 製作·評価

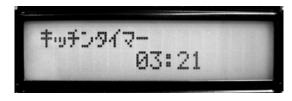

製作したタイマー付きディジタル時計は, 正常に動作することが確認できた。実際に 表示した画面を図2と図3に示す。

図 2. 12 時間表示

図 3. キッチンタイマー

時計・タイマー共に正常に表示され、使用する上では全く問題なかった。ドットマトリックス LED も問題なく動作した。

今後の課題としては、スイッチの操作性能の向上が挙げられる。今回は、6個のスイッチを使用した。今後、スイッチの数をより少なく、効率良く操作できるものが求められる。

#### 4. まとめ

本研究を通して、VHDLによるディジタル回路の設計手法を学ぶことができた。同時に、FPGA・CPLDへ実装することで、実装方法の基礎を学ぶことができた。