# 欠陥を作り込んだLSIの特異なIDDQ変動

# 高知工科大学 システム工学群 電子工学専攻 真田研究室 1150153 森津房貢

### 1.はじめに

本研究は、LSIの劣化兆候を検知することを目的とする。故障解析の分野では、原因場所の特定や、劣化兆候の検知などがある。本研究は、LSIに熱によるストレスを加え、劣化の加速を促し、電源電流(IDDQ値)の変化によって解析してく。また、検知方法として、相関関数を用いて角度による検知を行い、経過を収集していくのを研究テーマとした。

# 2.実験手順

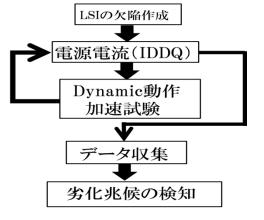

図1の順に研究を行っていく。 最後の劣化の兆候を検知するために、収集したデータを相関係数で顕在化する。(1)式

$\theta = \arccos(r)...(1)$

を用いる。

図1 実験フロー

#### 3. 実験結果

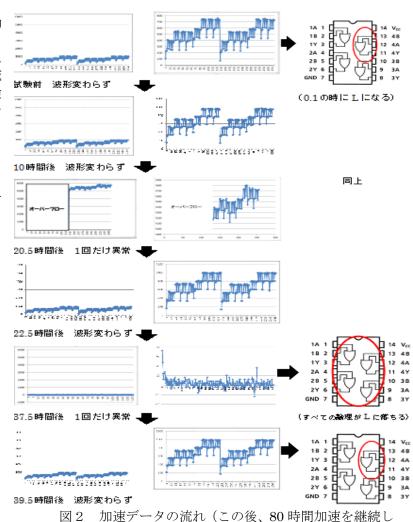

120°C、8 v で 2 時間置きに計測することにした。その結果、20.5 時間後に変化が見られた。しかし、256 パターンで 256 回の IDDQ を測り、128 パターン目までは完全にショートとみられる OverFlow とでた。そこで、2 時間確認のために加速試験行った。すると、試験前と値があまり変わらない正常の値を返した。再度試験を再開した。再開してからは試験前と変わらず、さらに 20 時間、2 時間置きに計測した。また、37.5 時間後に論理はすべて L に落ちグラフも変化が見られた。(図 2)再度試験を行うと、試験前データと近くなり論理も元に戻る。ここから約 40 時間試験前データと近いデータが続いた。そして、89.5 時間後に 37.5 時間後と同じ変化が見られ、論理もすべて L に落ちていた。確認のためさらに 2 時間加速させたが、試験前と同じ値に戻った。故障に至るまで数回論理が異常をきたす。

凶2 加速テータの流れ(この後、80 時間加速を継続し て行っている)

## 4.まとめ

加速試験を通して、LSI は劣化に至るまでに、20.5 時間後や37.5 時間後、89.5 時間のような IDDQ 値の増加や論理異常を起こす。しかし、再度加速させると、試験前データの値と近くなり、戻ることが判明した。この現象は、他の LSI も起こる。LSI 自体が、チップの破損やピンが折れるといったことが起こらない限り、急に故障することが少ないのではないかと考えられる。だが、劣化の顕在化という面では、明確な実測データが得られなかった。今後の課題として、劣化によって IDDQ 異常、論理異常をもたらした回路が回復する現象について注目していきたい。それは、一般に考えられることとして、一度劣化によってすべての出力が L に変化することはショートに違いないからである。