# 2 段オペアンプを用いた BGR に対する BIST 手法の検討

## 橘研究室 1170051 窪添 諒

# 1. はじめに

BIST (Built-In Self-Test) とは、テスト容易化設計 (DFT: Design For Testability) 技術の1つで、LSI テスタの機能である、テスト入力発生とテスト応答解析を行う回路をチップ内に組み込んでおく手法である。BIST により、LSI テスタにかかるコストとテストの時間的コストを削減することができる。現在、デジタル回路における BIST は既に実用化されているが、アナログ回路に対する BIST は回路素子のばらつき、統一的な手法の確立が難しいといった問題から未だ実用化に至っていない。そこで本研究では、アナログ・デジタル混載 LSI において基準電源回路として機能する BGR (Bandgap Reference)と呼ばれるアナログ回路に対する BIST の提案を研究目的とした。

### 2. BIST の対象とした BGR

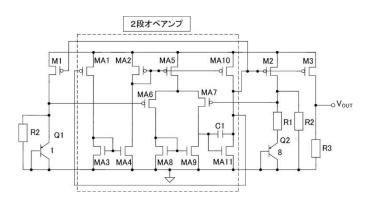

図 1 に、BIST の対象とした、 2 段オペアンプを用いた BGR の回路図を示す。この BGR の 14 個の MOSFET のカタストロフィック故障 (端子のオープン、端子同士のショート) を BIST の故障検出対象とした。

図1 BIST の対象とした BGR

### 3. 提案 BIST

図1のBGRに対するBISTの故障検出方法を以下に示す.

- 1. 特定のノードの電圧を正常値と比較し、故障を判別する.

- 2. 1 で検出できなかった故障については、オペアンプのバイアス回路部の MA4 にテスト入力を加えて、そのときの正常出力値と比較することにより故障を判別する.

- 3. M3 の GDS を検出するために M3 のゲート電圧を 0V に して, その時の正常出力値と比較する.

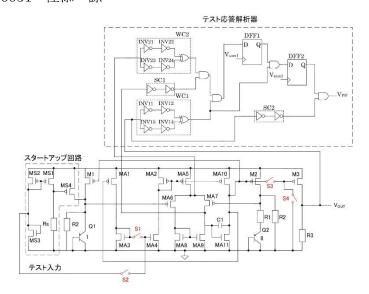

図2に、これらの故障検出方法を実装したBIST回路を示す。 BGRのスタートアップ回路にテスト入力発生機能を持たせ、 スイッチの切り替えにより MA4 へのテスト入力を行っている.

図 2 BISTの回路実装

このような構成にすることにより、小面積化が可能になる. M3 のゲートとグランドを、スイッチを介して接続できるようにしている. 最終的なテスト出力は、テスト応答解析器より High もしくは Low の論理値で出力される.

提案 BIST の性能について、故障検出率は 92.6% (75/81)、面積オーバーヘッドは 8.8%であった。表 1 に、BIST 回路を付加した場合と付加していない場合の BGR の性能比較を示す。これより、BIST 回路は BGR に対して負荷となっていないことがわかる。

チップを実測した際、故障無しの BGR について、正しいテスト結果が出力されていなかった。これは、BGR、ウィンドウコンパレータの MOSFET のばらつきにより、ノードの電圧がウィンドウコンパレータの入力電圧範囲を外れてしまったことが原因と考えられる。

| 性能                     | シミュレーション値     |             |

|------------------------|---------------|-------------|

|                        | BGR(BIST回路なし) | BIST回路付加BGR |

| 出力電圧(@VDD=1.8V)        | 1.115V        | 1.115V      |

| 出力電圧変動(@VDD=1.6V~2.0V) | 0.0075V       | 0.0075V     |

| 温度係数(0°C~100°C)        | 25ppm/°C      | 24.2ppm/°C  |

表 1 BGR の性能比較

#### 4. まとめ

2 段オペアンプを用いた BGR に対して,高い故障検出率,低い面積オーバーヘッド,また BGR の負荷とならない BIST を作製できた.今後,チップを確実に動作させるために,BGR,ウィンドウコンパレータの MOSFET のばらつき耐性の向上,またウィンドウコンパレータの入力電圧範囲を広く取れるノードを探すことが対策として必要である.