# 多オペランド積和演算アクセラレータのテストチップ測定

1180048 兼本 一生 (集積システム研究室) (指導教員 密山 幸男 准教授)

## 1. はじめに

近年,機械学習をはじめとして膨大な演算量を必要とするアプリケーションが注目されており,それらの処理を効率的に処理する集積回路について広く研究が行われている。特に,膨大な積和演算の高効率実行が求められているが,GPU やFPGA では消費電力や回路規模の面で課題がある。

積和演算や多項加算の高効率実現を目的として、カウンタを基本要素とする演算器の有効性が報告されている[1]. そこで本研究では、先行研究で作成されたアクセラレータのテストチップ 2 品種(1607 チップ、1702 チップ)の動作確認及び消費電流を、チップ評価用 FPGA ボード(MU300-EM4)を用いて測定し、消費エネルギーを評価する.

## 2. 提案アクセラレータの構成

部分積生成 (PPG)

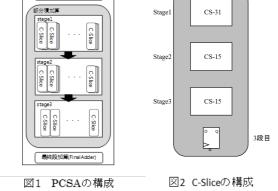

提案アクセラレータ PCSA (Programmable Counter Slice Array) は、部分積生成、部分積加算、最終段加算で構成される。このうち部分積加算部を、カウンタを基本要素とする回路で構成する[2]. 図 1 に PCSA の基本構成を示す。PCSA は、入力数の異なる3種類のカウンタを縦列接続した C-Slice をさらに3 段接続 (Stage-1~3) させることにより、大規模な多項加算演算を効率よく実行できるよう構成されている。C-Slice の種類により、C-Slice 多段接続時の並列数が決まる。本研究で用いる C-Slice は、最も効率の良い CS-31/CS-15/CS-15 の構成になっている。C-Slice の構成を図 2 に示す。

# 3. 試作チップの仕様

1607 チップと 1702 チップの仕様を表 1 に示す。 1702 チップは 1607 チップを改良したチップで、回路面積が小さくなり積和演算ビット幅が可変となった。

表1 チップの仕様

|         | 1607チップ | 1702チップ         |           |           |           |  |

|---------|---------|-----------------|-----------|-----------|-----------|--|

| 演算ビット幅  | 12bit   | 18bit           | 12bit     | 9bit      | 8bit      |  |

| 積算項数    | 108個    | 108個            | 108個×2セット | 108個×3セット | 108個×4セット |  |

| ライブラリ   | 65nm LP |                 |           |           |           |  |

| 電源電圧    | 0.4V    | 0.75V<br>100MHz |           |           |           |  |

| 日煙動作用波数 | 100MHz  |                 |           |           |           |  |

1607 チップには 4 種類の動作モード, 1702 チップには 4 種類の動作モードと 4 種類の CS 入力モードが存在する. 動作

モードやCS入力モードを決められた手順で操作することで、 LFSRによりオペランドを生成し、積和演算を実行する.その 演算結果を CRC チェックサムで確認することで基本動作の 確認が可能となっている.

#### 4. テストチップの測定結果

1607チップと1702チップの動作確認の結果を表2に示す.

表2 動作確認結果

表3 測定消費電流

| 動作周波数[lz] | 動作<br>1607チップ 1702チップ |   | 動作周波数<br>[Hz] | 消費電流<br>[mA] |

|-----------|-----------------------|---|---------------|--------------|

| 100k      | 0                     | × | 100k          | 0.01         |

| 1M        | 0                     | × | 1M            | 0.04         |

| 10M       | 0                     | × | 10M           | 0.28         |

| 20M       | 0                     | × |               |              |

| 30M       | 0                     | × | 20M           | 0.292        |

| 40M       | 0                     | × | 30M           | 0.86         |

| 50M       | Δ                     | × | 40M           | 1.15         |

表 2 より、1607 チップにおいて動作周波数 50[MHz]の時に動作する場合としない場合があった。また、1702 チップは正常動作しなかった。

1607 チップの測定消費電流値を表 3 に示す. 1607 チップの電流値測定は、チップ評価用 FPGA ボードとソースメータ (Source Measure Unit: SMU) を用いて行った. 動作周波数 10[MHz]の時、消費電流 0.28[mA]となり、電圧が 0.4[V]であることから、12 ビット 216 オペランド積和演算 1 回あたりの消費エネルギーは 11.2[pJ]となった.

一方、12 ビット 216 オペランド積和演算器を Verilog-HDL で記述し、Synopsys 社 Design Compiler で論理合成した結果、消費電力は動作周波数 50[MHz]で 667.2[μW]となり、演算 1 回あたりの消費エネルギーは 13.34[pJ]となった. これにより、提案アクセラレータの消費エネルギーは専用回路と同等であることがわかった. しかし、テストチップの実測値は部分積生成部の消費エネルギーを含んでいないため、これを含むと専用回路より消費エネルギーが大きくなる可能性もある.

## 5. 結論

1607 チップと 1702 チップの動作確認を行うとともに、1607 チップの消費エネルギー評価を行った. 測定結果より、提案アクセラレータの消費エネルギーは ASIC と同等であることがわかった. 今後の課題として、1702 チップが正常動作しない原因の調査を行うとともに、改良版チップの作成に取り組む.

# 参考文献

[1] A. Cevrero, et al., "Field Programmable Compressor Trees: Acceleration of Multi-Input Addition on FPGAs," ACM Trans. Reconfigurable Technology Systems, vol. 2, pp. 13:1-13:36, June 2009.

[2] 風谷亮多, "大規模積和演算アクセラレータの設計" 高知工科大学卒業研究報告, 2017年2月