## 2 次 Δ Σ 変調回路の設計

# Design of Second-Order Delta-sigma Modulator

1190021 上村 大輔 (大規模集積回路研究室) (指導教員 橘 昌良 教授)

#### 1. はじめに

A/D・D/A 変換技術が必要とされていく中で信号雑音比 (S/N), ノイズフロアは A/D・DA 変換の精度の良さを表す基準になっている. 例えばデジタルオーディオプレーヤーでは 1 標本化 16 ビットを 1 ロードとしており高精度な S/N 比を必要としている. [1]

Nauta OTA を用いた連続型、離散型の 2 次  $\Delta$   $\Sigma$  変調器を設計し、先行研究[2]よりも高い S/N 比、ノイズフロアを算出することを目的とする.

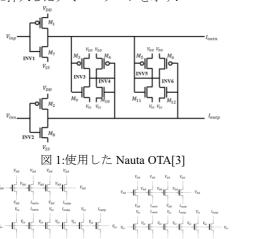

#### 2. 使用した Nauta OTA

図 1 に今回使用した Nauta OTA の回路図を図 2, 図 3 に $V_{inp}$  側 $V_{inn}$ 側に挿入したダミーパターンを示す.

図  $2:V_{inp}$ 側のダミーパターン[3] 図  $3:V_{inp}$ 側のダミーパターン[3]

### 3. Nauta OTA を用いた 2 次 ΔΣ 変調器の構成

#### 3.1 連続型 2 次 ΔΣ 変調器

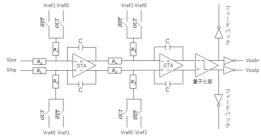

図 4 に本研究で設計した連続型 2 次  $\Delta\Sigma$  変調器の回路図と表 1 に設計した連続型  $\Delta\Sigma$  変調器の仕様を示す. 1 次側の出力とフィードバックのタイミングにズレが生じたため 2 次側のフィードバックに遅延をもたせ、タイミングを合わした.

図 4:設計した連続型 2 次 ΔΣ 変調器表 1:連続型 2 次 ΔΣ 変調器の仕様

| パラメータ     | 数值         |

|-----------|------------|

| С         | 8[pF]      |

| $R_1$     | 100[kΩ]    |

| $R_2$     | 50[kΩ]     |

| VDD       | 1.8[V]     |

| VSS       | 0[V]       |

| 入力範囲      | 0.6~1.2[V] |

| 信号帯域      | 22[kHz]    |

| サンプリング周波数 | 11.26[MHz] |

| Vref1     | 1.35[V]    |

| Vref0     | 0.45[V]    |

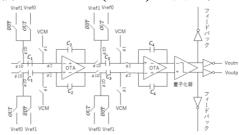

#### 3.2 離散型 2次 ΔΣ 変調器

図 5 に本研究で設計した離散型 2 次  $\Delta\Sigma$  変調器の回路図と表 2 に設計した離散型  $\Delta\Sigma$  変調器の仕様を示す. アナログスイッチのタイミングが同時にオンとならないように入力側のスイッチに遅延をもたせた. また, 1 次側を 0.5 倍, 2 次側を 2 倍の出力にしてノイズが $(1+z^{-1})^2$ になるようにした. [4]

図 5:設計した離散型 2 次 ΔΣ 変調器表 2: 離散型 2 次 ΔΣ 変調器の仕様

| パラメータ          | 数值         |

|----------------|------------|

| $C_1$          | 4[pF]      |

| $C_2$          | 8[pF]      |

| $C_3$          | 8[pF]      |

| C <sub>4</sub> | 4[pF]      |

| VDD            | 1.8[V]     |

| VSS            | 0[V]       |

| 入力範囲           | 0.6~1.2[V] |

| 信号帯域           | 22[kHz]    |

| サンプリング周波数      | 11.26[MHz] |

| Vref1          | 1.35[V]    |

| Vref0          | 0.45[V]    |

| VCM            | 0.9[V]     |

|                |            |

#### 4. シミュレーション結果

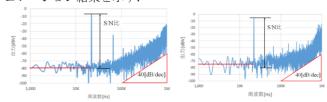

図 6, 図 7 に連続型,離散型の 2 次  $\Delta\Sigma$  変調器の FFT シミュレーション結果を示す.

図 6:連続型  $\Delta\Sigma$  変調器の FFT 結果 図 7:離散型  $\Delta\Sigma$  変調器の FFT 結果

## 5. まとめ

本研究では先行研究をもとに連続型、離散型の 2 次  $\Delta$   $\Sigma$  変調器の設計を行った。図 6、図 7 より、連続型、離散型の両方で先行研究よりも高い S/N 比をシミュレーション内で算出することができたが、離散型のノイズフロアが先行研究に比べ 5dBV 大きい結果になった。

#### 参考文献

- [1] 相良 岩男 "A/D·D/A 変換回路入門" 日韓工業新聞社 2003

- [2] 岡崎 泰士 "Nauta OTA を用いたΔΣ変調器の設計 と評価"高知工科大学 システム工学群 基盤工学専攻 2018

- [3] 軽野 滉士 "Nauta OTA の設計" 高知工科大学 システム工学群 電子工学専攻 2017

- [4] R.Schreier,G.C.Temes, " $\Delta \Sigma$ 型アナログ/デジタル変 換器入門" 和保 考夫, 安田 彰 監訳 丸善株式会社 2007