# 多オペランド積和演算アクセラレータのエネルギー効率評価

Energy Efficiency Evaluation of Multi Operand Multiply-Accumulate Accelerator

1225066 兼本 一生 (集積システム研究室)

(指導教員 密山 幸男 准教授)

#### 1. はじめに

機械学習では膨大な演算量が必要であり、特に積和演算の 高効率実行が求められている. そこで、積和演算や多項加算 の高効率実現を目的として、カウンタを基本要素とする演算 器の有効性が報告されている[1].

本研究では、膨大な積和演算の高効率実行を目的として提案されたアクセラレータの有効性を示すため、その基本動作を確認するために作成されたプロトタイプチップと、オペランドビット幅を可変にした改良版チップを用いて消費電流の測定を行った。さらに、FPGAとの比較評価を行うために単純積和演算回路をFPGAに実装して消費電流を測定した。評価には、積和演算1回あたりの消費エネルギーを用いた。また、専用回路との比較評価を行うため、論理合成による電力見積もりに基づく評価も行った。

### 2. 提案アクセラレータ

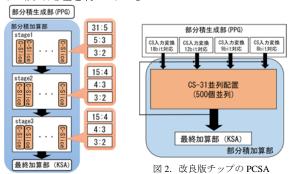

提案アクセラレータである PCSA(Programmable Counter Slice Array)[2]は、部分積生成部、部分積加算部、最終加算部で構成されている。部分積生成部は LFSR を用いて生成された乱数から部分積を生成している。2 種のチップの PCSA の構成を図 1 と図 2 にそれぞれ示す。部分積加算部はカウンタを基本要素とした回路で構成される。 最終加算部は KSA(Kogge-Stone Adder)[3]を使用している。PCSA の部分積加算部には入力数の異なる 3 種のカウンタを縦列接続した C-Slice を使用している。プロトタイプチップの PCSA では、C-Slice を3 段接続させることで,膨大な部分積を高速に圧縮できる。また、改良版チップの PCSA では CS-31 を 500 並列にし、オペランドビット幅に応じて使用個数を変えることでオペランドビット幅が可変としている。部分積加算部をループさせて 2 段で処理を行っている。

図1. プロトタイプチップの PCSA

#### AI. JETTINI JOHNSK

# 3. プロトタイプチップを用いたエネルギー効率評価

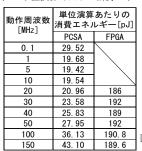

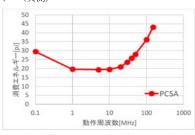

プロトタイプチップを用いて、各動作周波数における最低動作電圧で消費電流を測定し、消費エネルギーを算出した。また、FPGA との比較評価のため、プロトタイプチップと同じ演算を行う単純積和演算回路のRTL 記述を Verilog HDL で作成し、試作チップと同じ 65nm プロセスである Altera 社のStratixIIIに実装して動作時の消費電流を測定した。算出した消費エネルギーを表 1 と図 3 に示す。FPGA を用いた実測では、LSI テスタの仕様から動作周波数が 20MHz~150MHz のみの測定となっている。

動作周波数が 0.1kHz の時の PCSA の消費エネルギーが他の動作周波数と比べて大きくなった理由として, リーク電流の影響が考えられる. また, 動作周波数が 5MHz で電圧 0.328Vの時, 消費エネルギーが 19.42[pJ]で最小となった.

論理合成結果は PCSA が 10.487[pJ], 単純積和演算回路が 12.390[pJ]となり、実測時と同様に PCSA の方が消費エネルギーは小さくなることが確認できた.

表 1. 単位演算あたりの消費エネルギー (実測)

図3. 単位演算あたりの消費エネルギー (実測)

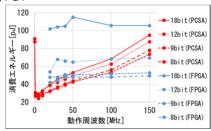

## 4. 改良版チップを用いたエネルギー効率評価

改良版チップについてもプロトタイプチップと同様の比較評価を行った. PCSAと FPGAによる単位演算あたりの消費エネルギーを図4に示す.LSIテスタの仕様により,単純積和演算回路が20MHz~150MHzのみの測定となっている.

動作周波数 0.01kHz と 0.1kHz の時の PCSA の消費エネルギーが他の動作周波数の時と比べて大きくなっているのはリーク電流の影響である. また, 動作周波数が 5MHz で電圧 0.37V の時, 消費エネルギーが 29.08[pJ]で最小となった.

論理合成による見積もり結果を用いた比較評価では、単純積和演算回路の方が、消費エネルギーが小さくなることが分かった.ただ、単純積和演算回路は、ビット幅ごとに異なる回路が必要であるのに対して、PCSAは1つの回路で異なるビット幅の演算が可能であることを考えると、有効性はあると考えられる.

図 4. 単位演算あたりの消費エネルギー (実測)

表 2. 単位演算あたりの消費エネルギー (論理合成)

|          | 単位演算あたりの消費エネルギー[pJ] |        |        |        |

|----------|---------------------|--------|--------|--------|

|          | 18bit               | 12bit  | 9bit   | 8bit   |

| PCSA     | 39. 07              | 18. 35 | 11. 74 | 9. 846 |

| 単純積和演算回路 | 17. 70              | 6. 513 | 3. 400 | 2. 674 |

#### 5. 結論

2 種の試作チップの消費電流の測定とエネルギー効率の評価を行った. 実測結果では単純積和演算回路に比べて, PCSA の方が低消費エネルギーであることが分かった.

## 参考文献

[1] A. Cevrero, et al., "Field Programmable Compressor Trees: Acceleration of Multi-Input Addition on FPGAs," ACM Trans. Reconfigurable Technology Systems, vol. 2, pp. 13:1-13:36, June 2009.

[2] 風谷亮多,"大規模積和演算アクセラレータの設計"高知工 科大学卒業研究報告, 2017年2月

[3] P.M.Kogge and H.S.Stone, "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equation", IEEE Transaction on Computers, Vol.22, No.8, Aug. 1973.