# セルフタイム型複合データ転送制御回路の FPGA 実装用タイミング検証法

1210306 尾ノ井 嶺卓 【 コンピュータ構成学研究室 】

# 1 はじめに

近年、多様な IoT(Internet of Things) デバイスを安価に柔軟に実現するために FPGA(Field Programmable Gate Array) が活用されている。セルフタイム型パイプライン STP(Self-Timed Pipeline) により実現されたデータ駆動型プロセッサ DDP(Data-Driven Procesor) は、データの到着をトリガとして多重並列処理を実行するため、高性能で省電力な IoT 向き FPGA コアの実現法として有望である。これに対して、先行研究 [1] では、基本的な STP を FPGA 実装するためのタイミング検証法が提案されている。本研究では、この検証法を拡張して、DDP の実行制御に必要な複合データ転送制御回路のタイミング検証法を検討した。

### 2 STP におけるデータ転送制御回路

STP 内の各パイプライン段では、隣接する C 素子間でデータ転送要求 (send) 信号を送信し、次段の C 素子がデータ転送許可 (ack) 信号を返信した場合に、局所的なクロック信号 CP を生成して、データラッチ DL を開放する(データ転送する). よって、send 信号/ack 信号の授受と CP 生成のタイミングが、ラッチのセットアップ/ホールド時間制約を満たす必要がある.先行研究では、C 素子内の NAND ゲートを疑似クロック入力付き LUT に置換することによって、FPGA 設計ツールから検証すべきパスのタイミング情報を抽出する.しかし、STP の分流制御素子 CB やパケット複製消去制御素子 CX2 のような複合データ転送制御回路の動作を保証するためには、新たなタイミング制約条件を追加して検証する必要がある.

### 3 複合転送制御回路のタイミング検証

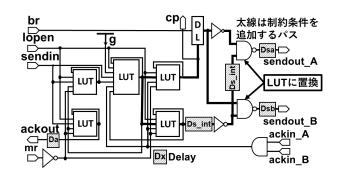

CB, CX2内の全ての AND, OR, NAND ゲートの正しい入力/出力信号値を調査し、CB, CX2の send/ackが正しい信号値を出力するための新たな制約条件の追加と、DDPのデータパス側にある DLのセットアップ/ホールド時間制約を満たすような拡張を行った.制約条件に従い、回路内でタイミング情報の抽出が必要なパスの端点の論理ゲートを LUT に置き換えることで、図 1のような回路に修正する.

また、新たなタイミング制約条件の検証に対応するため、タイミング情報を計測するための制約ファイル、設計した回路の検証したいパスを指定する json スクリプトの記述法と、指定したパスとタイミング情報をもとにタイミング違反を判定するプログラムを拡張する.

図 1 タイミング検証可能な CB 回路

# 4 検証結果・まとめ

上記の手法で設計した CB と CX2 をそれぞれ C 素子と連結し、DL 間のデータの転送とロジックでの処理を行う 2 段パイプライン回路を設計した。設計した回路をIntel 社 FPGA の MAX-10 に実装し、ツールを用いてタイミング検証を行った。検証時、パイプライン前段のCP の立ち上がりから後段の CP の立ち上がりまでの時間 (Tf) と、後段の CP の立ち上がりから前段の CP の立ち上がりまでの時間 (Tr) を測定し、各 DL のセットアップ/ホールド時間制約を満たしていることが表 1 より確認できた。

表 1 CB, CX2 の拡張した制約条件の検証結果

|        | $CB^1$ | $CB^2$ | $CX2^3$ | $CX2^4$ | $\mathrm{CX}2^{56}$ |

|--------|--------|--------|---------|---------|---------------------|

| Tf(ns) | 27.4   | 26.2   | 21.2    | 38.2    | 27.7                |

| Tr(ns) | 6.06   | 6.07   | -       | 5.79    | -                   |

同じく追加した制約条件について、2本のパス (Ss, Sl) の到着時間の計測と大小関係の比較によるタイミング検証ができており、複合データ転送制御回路 (CB, CX2) に必要な制約条件がすべて検証できていることを確認した、今後の課題として、DDP に用いられる他の複合データ転送制御回路 CM, CE についての検証法の拡張が残されている.

#### 参考文献

[1] S. Yoshikawa, et al., "Pipeline Stage Level Simulation Method for Self-Timed Data-Driven Processor on FPGA," iEECON, pp. 1–5, Mar. 2020.

<sup>&</sup>lt;sup>1</sup>出力先が A の場合.

<sup>&</sup>lt;sup>2</sup>出力先が B の場合.

<sup>3</sup>消去機能,複製機能ともに使用していない場合.

<sup>4</sup>複製機能のみ使用している場合.

<sup>5</sup>消去機能のみ使用している場合.

<sup>6</sup>消去機能,複製機能ともに使用している場合.