# CMOSでのオペアンプの設計と測定

## Operational amplifier design and measurement in CMOS

1230140 平谷優太 (回路工学研究室)

(指導教員 橋 昌良 教授)

### 1. はじめに

オペアンプは集積回路(LSI:Large-Scale Integration)アナログ回路で中心的な役割を持つ重要な回路である。オペアンプ単体では増幅回路として機能するが、周辺回路と組み合わせることで様々な機能を持たせることができる回路である。先行研究ではオペアンプを使用した回路の設計、評価を行ってきた。本研究ではオペアンプ単体の設計、評価を行い、より優れたオペアンプの設計を目指す。

### 2. オペアンプとは

オペアンプ(Operation Amplifier: 演算増幅器)とは回路記号図 2.1 のように表わされる非反転入力端子と反転入力端子間の差分を増幅し出力する回路である。基本的なオペアンプは作動増幅回路とソース設置回路を組み合わせた 2 段構成オペアンプである。トランジスタをカスコードにしたりすることでテレスコピックオペアンプという 1 段構成でも 2 段構成並みの利得を持つオペアンプも存在する。

図 2.1 オペ

アンプの

回路記号

### 3. オペアンプの設計

オペアンプの回路設計は IC.ver 6.14 で回路の設計を Rohm 0.18  $\mu$ m テクノロジで行い、HSPICE でシミュレーションを行い、Cosmos Scope で観測し、Calibre で LVS/DRC 検証を行った。

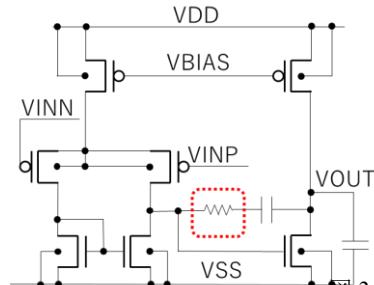

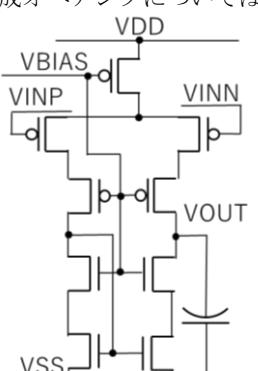

設計した 2 段構成オペアンプおよびテレスコピックオペアンプを図 3.1、図 3.2 に示す。2 段構成オペアンプについては作動増幅回路とソース接地回路の間に抵抗の有無で 2 種類設計を行った。

図 3.1 2 段構成オペアンプ

図 3.2 テレスコピックオペアンプ

### 4. 測定結果

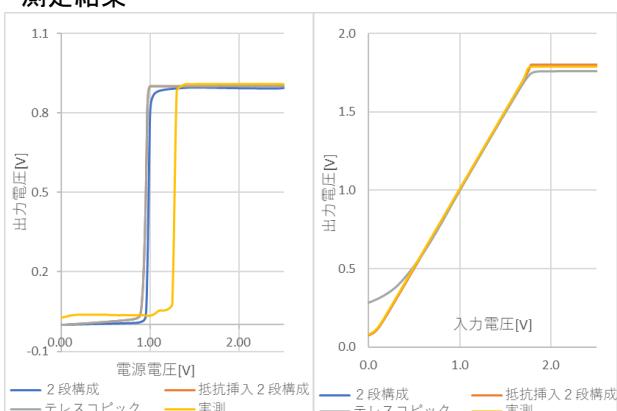

図 4.1 動作電源範囲

図 4.2 出力範囲

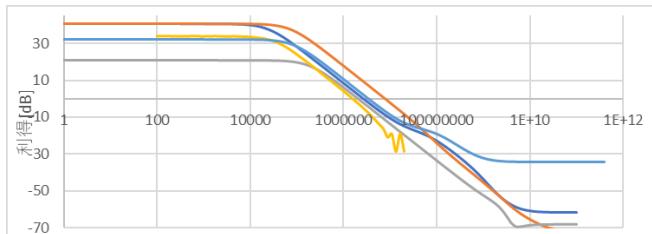

図 4.3 電圧利得

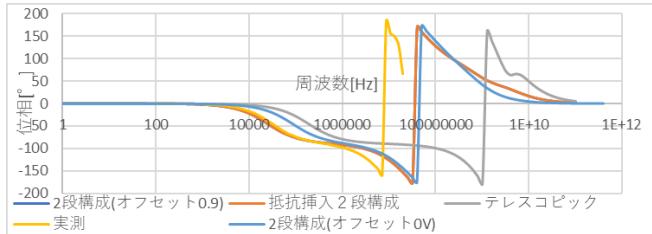

図 4.4 位相

図 4.1 に入力を 0.9V で固定して電源電圧を変化させたときの出力、動作電源範囲を示す。図 4.2 に電源電圧を固定して入力電圧を変化させたときの出力、出力範囲を示す。図 4.3、図 4.4 に入力を 100mV オフセット電圧 0.9V の周波数応答解析の結果を示す。ただし、測定機器がオフセット電圧を作れないため、実測及び 2 段構成(オフセット電圧 0)はオフセット電圧 0.0V で検証を行った。測定機器が 100Hz～20MHz しか出力出来ないため、実測のみ 100Hz～20MHz の解析となっている。

### 5. 考察

テレスコピックオペアンプで出力範囲が狭くなった理由について考察する。テレスコピックオペアンプは 2 段構成オペアンプと比べて VDD-VSS 間の MOSFET の数が多いため必要なオーバードライブ電圧が増える。それによって出力範囲が狭くなったと考えられる。

次に試作チップの動作電源範囲が狭い理由について考察する。シミュレーション値より動作電源範囲が狭い。そのため、レイアウトの段階で何かしらの問題があったと考えられる。

次に試作チップの帯域幅がシミュレーション値より低い理由を考察する。実測ではノイズが発生するため誤差が生じたと思われる。

### 6. まとめ

本研究ではオペアンプ単体の設計、評価を行い、より優れたオペアンプの設計を目的とした。そして 2 種類の 2 段構成オペアンプおよびテレスコピックオペアンプの評価としてシミュレーションおよび 2 段構成オペアンプの評価として実測を行った。2 段構成オペアンプに抵抗を挿入する事で利得、位相余裕、帯域幅の向上が見られた。今回作成した 1 段構成オペアンプは 2 段構成オペアンプの同程度の性能を引き出すことが出来なかった。試作チップの実測値はシミュレーション値より低いが、想定された条件での実測ではなかった。そのため別の実測方法の考案が今後の課題である。

### 参考文献

- [1]吉澤浩和著、「CMOS OP アンプ回路 実務設計の基礎」、CQ出版社、2007

- [2]岡村 健夫著、「OP アンプ回路の設計」、CQ出版社、1990

- [3]谷口研二著、「CMOS アナログ回路入門」 CQ出版社、2005