# CMOS オペアンプにおける電圧利得増幅の設計

# Design of Voltage Gain Amplification in CMOS Operational Amplifiers 1250087 鈴江陽大(回路工学研究室)

(指導教員 橘 昌良 教授)

#### 1. はじめに

オペアンプ単体では増幅回路として機能するが、周辺回路と組み合わせることで様々な機能を持たせることができる回路である。これまでの研究では、オペアンプを使用した回路の設計および評価が行われてきました。しかし、本研究では特にオペアンプ単体の設計とその評価に焦点を当て、より高い電圧利得を持つオペアンプの開発を目指します。具体的には、CMOS 技術を用いたオペアンプの設計に取り組み、その性能を徹底的に評価します。

# 2. オペアンプ

OP アンプは(operational amplifier)の略で、集積回路 (LSI:Large-Scale Integration)アナログ回路で中心的な役割を持つ増幅回路である。オペアンプの回路記号を示す。図1のように、オペアンプには2本の入力端子(反転入力、非反転入力)と1本の出力端子があり、入力端子間の電圧の差を増幅し出力するのがオペアンプの基本的な性質である。

図 1.1 オペアンプの回路記号

#### 3. オペアンプの設計

オペアンプの回路設計は IC. ver 6.14 で回路の設計を RohmO.  $18\,\mu\,\mathrm{m}$  テクノロジで行い、HSPICE でシミュレーションを行い、Cosmos Scope で観測し、Calibre で LVS/DRC 検証を行った。

設計した2段構成オペアンプおよびテレスコピックオペアンプを図に示す。2段構成オペアンプは入力段をカスコード構造にしたものとそうでないものの2種類設計を行った。

図 2.1 2 段構成オペアンプ図 2.2 テレスコピックオペアンプ

## 4. 測定結果

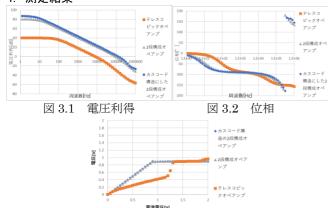

図 3.3 動作電源範囲

図3.4 モンテカルロシミュレーション

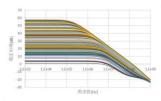

側の入力端子に周波数 1[kHz]で DC0.9[V]、AC1[V] を入力し、もう片側にこの逆相の電圧を加えた。電圧利得と周波数特性のシミュレーション結果を図 3.1、図 3.2 に示す。図 3.3 に入力を 0.9V で固定して電源電圧を変化させたときの出力、動作電源範囲を示す。本研究では、CMOS 技術を用いたオペアンプの電圧利得向上を目指し、最適な設計パラメータの特定とバイアス回路の設計を行った。しかし、チップの実測結果は期待した性能を達成できなかった。2 段構成オペアンプに対して、モンテカルロシミュレーションを 200 回実施し、トランジスタのパラメータ変動に伴う電圧利得のばらつきを確認した。その結果、図 3.4 より電圧利得が 1dB から約 60dB の範囲で大きく変動することが明らかとなった。

#### 4. 考察

本研究ではCMOS技術を用いてオペアンプの設計に取り組み、その電圧利得を評価した。しかし、チップの実測結果は期待した性能を達成できなかった。モンテカルロシミュレーションより実測に用いたチップが想定していた値にならなかったのは、設計時に使用したソフトウェア上のトランジスタモデルと、実際に製造されたチップ上のトランジスタとのパラメータに差異が生じたためと考えられる。

テレスコピックオペアンプは、その構造上、VDD と VSS 間に直列に接続される MOSFET の数が多くなる。各 MOSFET には閾値電圧とオーバードライブ電圧が必要であり、それらの合計が増加することで、全体の電圧マージンが減少する。その結果、トランジスタが適切に動作できる電源電圧の範囲が狭くなり、出力電圧のスイング幅も制限される。これが、2 段構成オペアンプと比較してテレスコピックオペアンプの動作電源範囲が狭くなった主な理由と考えられる。

### 5. まとめ

本研究により、トランジスタのパラメータ調整とカスコード構造の導入を通じて、オペアンプの電圧利得を大幅に向上させることができた。しかし、チップの実測において期待した性能を得られなかったことから、プロセスばらつきやバイアス回路設計、レイアウト設計など、複数の要因が性能に影響を及ぼしたことが考えられる。

今後は、これらの課題に対して具体的な改善策を講じ、信頼性の高いオペアンプの設計を目指す必要がある。ばらつきに強い設計手法の確立や、他の性能指標(周波数特性、消費電力など)との最適なバランスを追求することで、より実用的で高性能なCMOSオペアンプの実現に寄与できると期待される。

# 参考文献

[1]谷口研二 著、「CMOS アナログ回路入門」 CQ 出版社、 2005

[2]岡村 廸夫 著、「OP アンプ回路の設計」、CQ 出版社、1990 [3]吉澤浩和 著、「CMOSOP アンプ回路 実務設計の基礎」、CQ 出版社、2007